# Revision History 8Gb DDR4 AS4C512M16D4A Automotive grade - 96 ball FBGA PACKAGE

| Revision | Details         | Date     |

|----------|-----------------|----------|

| Rev 1.0  | Initial Release | Nov,2023 |

# 512M x 16 bit DDR4 Synchronous DRAM (SDRAM)

# Features

- JEDEC Standard Compliant

- Fast clock rate: 1600MHz

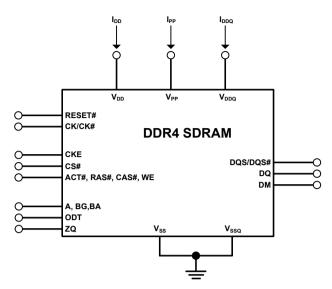

- Power supplies:

- V<sub>DD</sub> & V<sub>DDQ</sub> = +1.2V ± 0.06V

- V<sub>PP</sub> = +2.5V -0.125V / +0.25V

- Operating temperature:

Automotive: TC = -40~105°C

- Supports JEDEC clock jitter specification

- Bidirectional differential data strobe, DQS &DQS#

- Differential Clock, CK & CK#

- 8 internal banks: 2 groups of 4 banks each

- Separated IO gating structures by Bank Group

- 8n-bit prefetch architecture

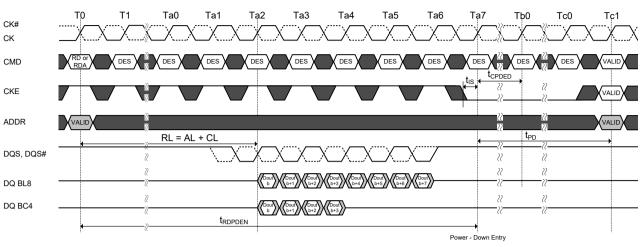

- Precharge & Active power down

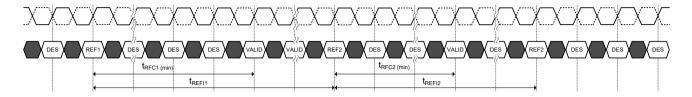

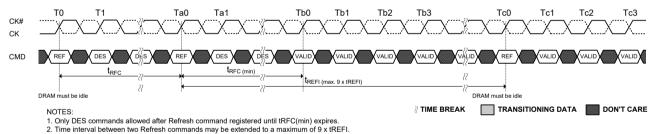

- Auto Refresh and Self Refresh

- Low-power auto self refresh (LPASR)

- Self Refresh Abort

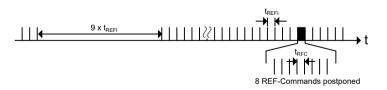

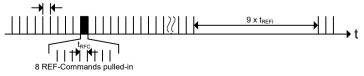

- Fine Granularity Refresh

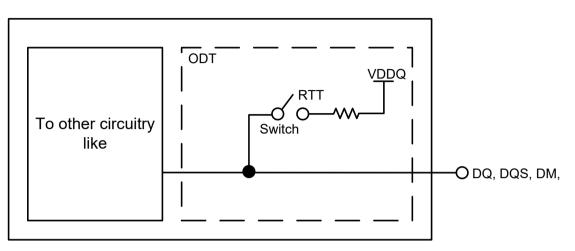

- Dynamic ODT (RTT\_PARK & RTT\_Nom & RTT\_WR)

- Write Leveling

- DQ Training via MPR

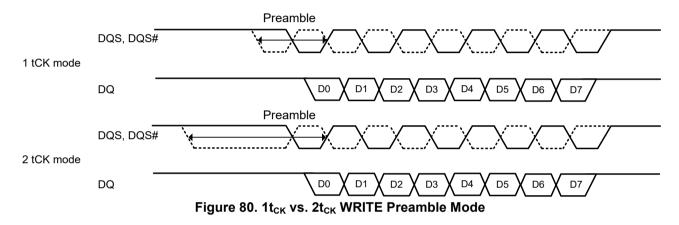

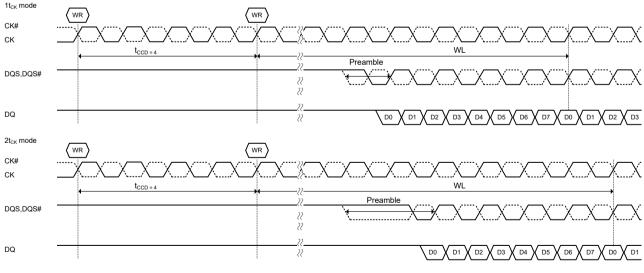

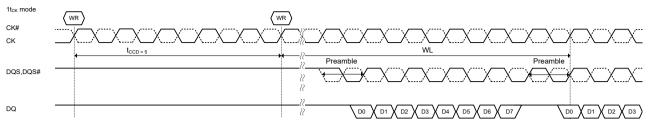

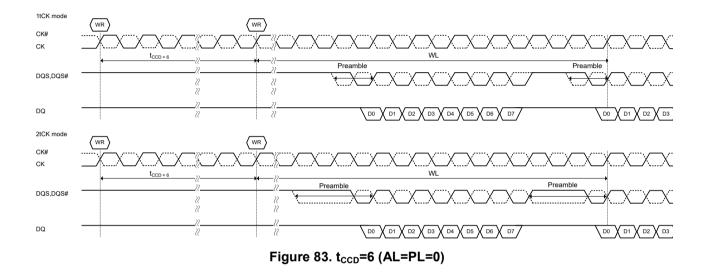

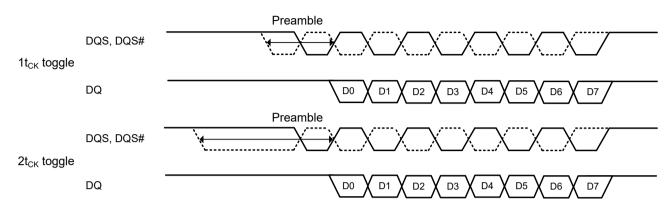

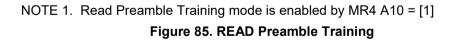

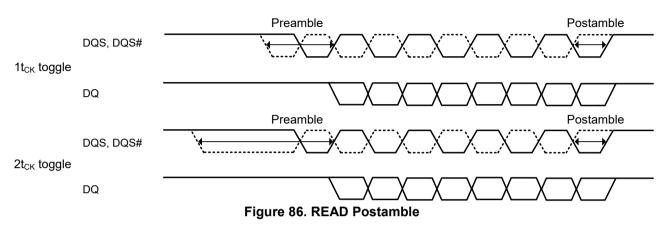

- $\bullet$  Programmable preamble is supported both of  $1t_{CK}$  and  $2t_{CK}$  mode

- Command/Address (CA) Parity

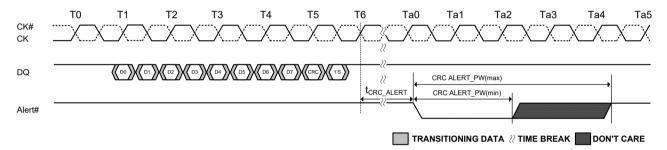

- Data bus write cyclic redundancy check (CRC)

- Boundary Scan Mode

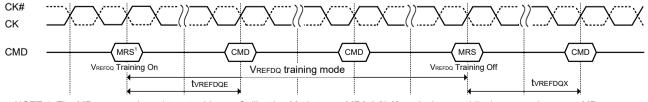

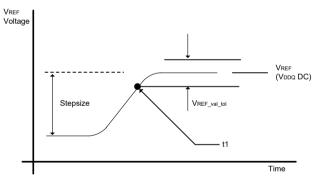

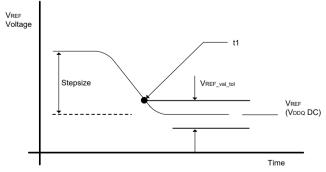

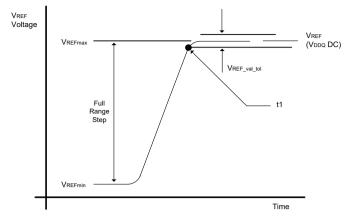

- $\bullet$  Internal  $V_{\text{REFDQ}}$  Training

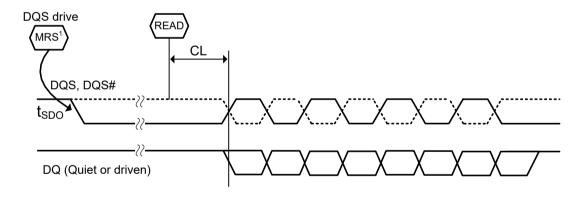

- Read Preamble Training

- Control Gear Down Mode

- Per DRAM Addressability (PDA)

- Output Driver Impedance Control

- Dynamic on-die termination (ODT)

- Input Data Mask (DM) and Data Bus Inversion (DBI)

- ZQ Calibration

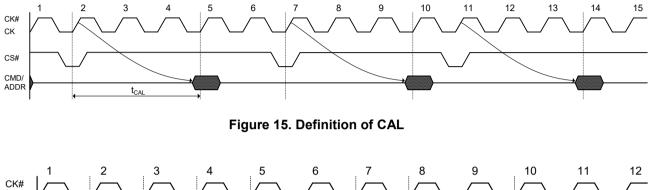

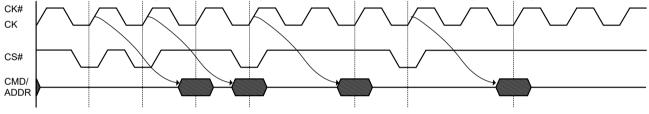

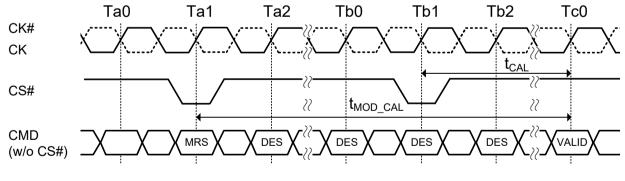

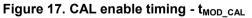

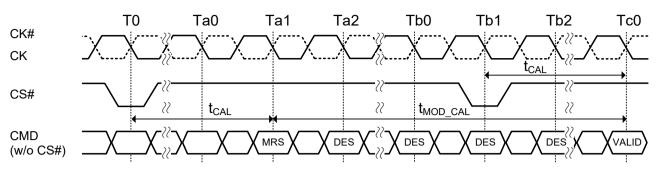

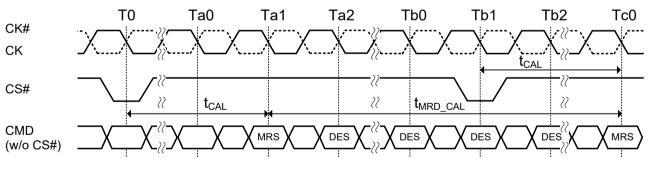

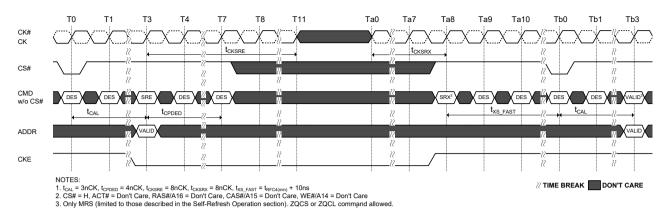

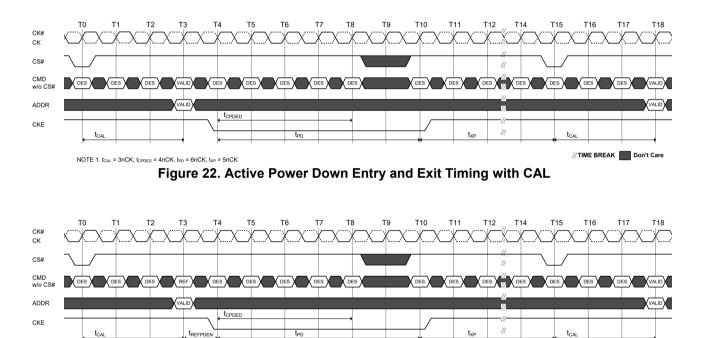

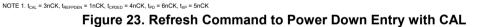

- Command/Address latency (CAL)

- Asynchronous Reset

- DLL enable/disable

- Burst Length (BL8/BC4/BC4 or 8 on the fly)

- Burst type: Sequential / Interleave

- CAS Latency (CL)

- CAS Write Latency (CWL)

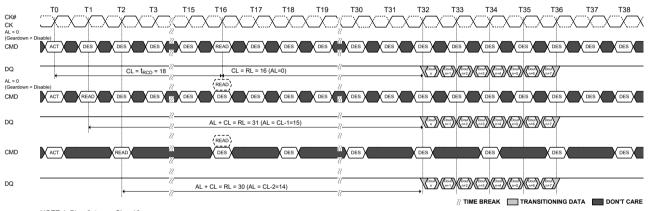

- Additive Latency (AL): 0, CL-1, CL-2

- Average refresh period

- 8192 cycles/64ms (7.8us at -40°C  $\leq$  T<sub>C</sub>  $\leq$  +85°C)

- 8192 cycles/32ms (3.9us at +85°C <  $T_C \leq$  +105°C)

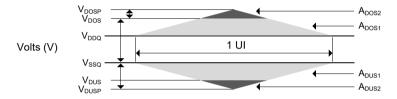

- Data Interface: Pseudo Open Drain (POD)

- RoHS compliant

- Hard post package repair (hPPR)

- Soft post package repair (sPPR)

- Package: Pb Free and Halogen Free

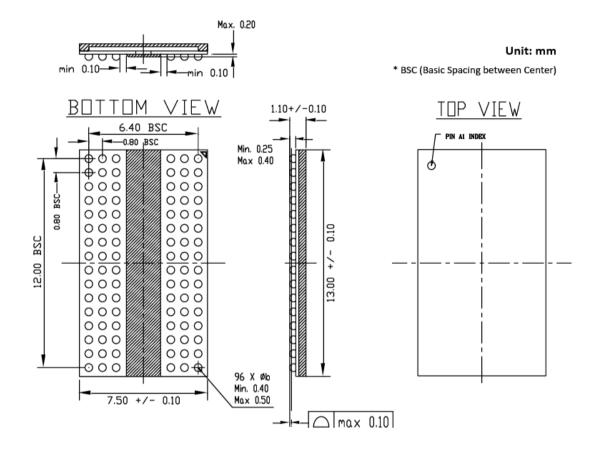

- 96-ball 7.5 x 13 x 1.2mm FBGA

#### Table 1. Ordering Information

| Product part No     | Org       | Temperature    | Max Clock<br>(MHz) | Package      |

|---------------------|-----------|----------------|--------------------|--------------|

| AS4C512M16D4A-62BAN | 512M x 16 | -40°C to 105°C | 1600               | 96-ball FBGA |

### Table 2. Speed Grade Information

| Speed Grade | Clock<br>Frequency | CAS Latency | tRCD(ns) | tRP(ns) |

|-------------|--------------------|-------------|----------|---------|

| DDR4-3200   | 1600 MHz           | 22          | 13.75    | 13.75   |

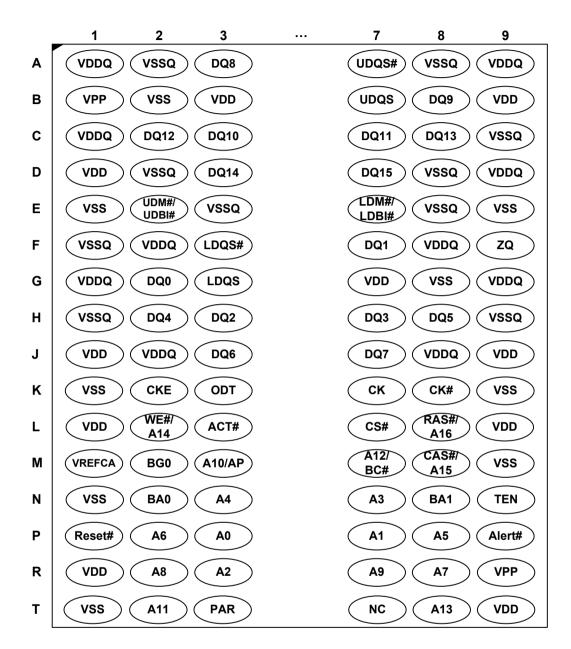

# Ball Assignment

Figure 1. 96-Ball (FBGA Top View)

AS4C512M16D4A-62BAN

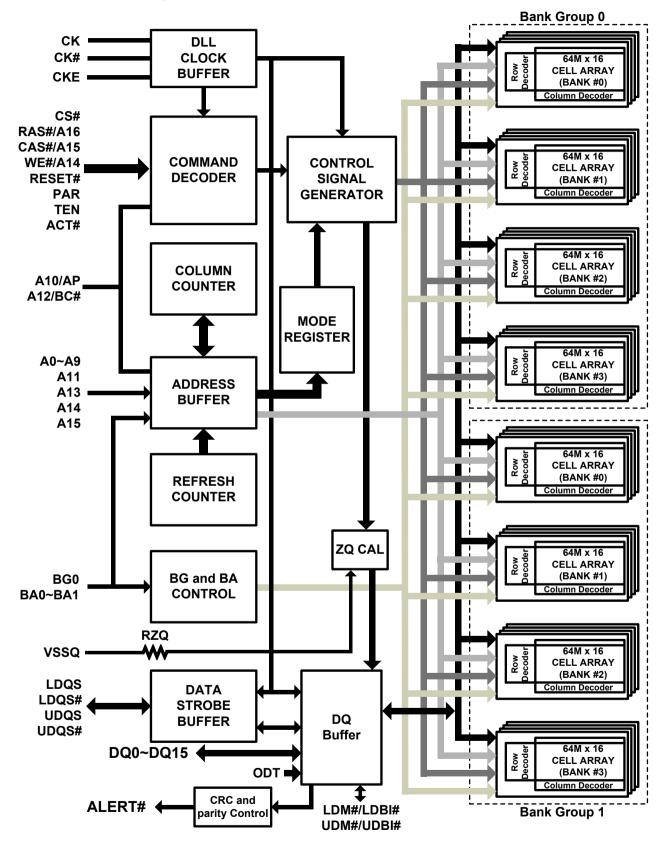

# Functional Block Diagram

Figure 2. Block Diagram

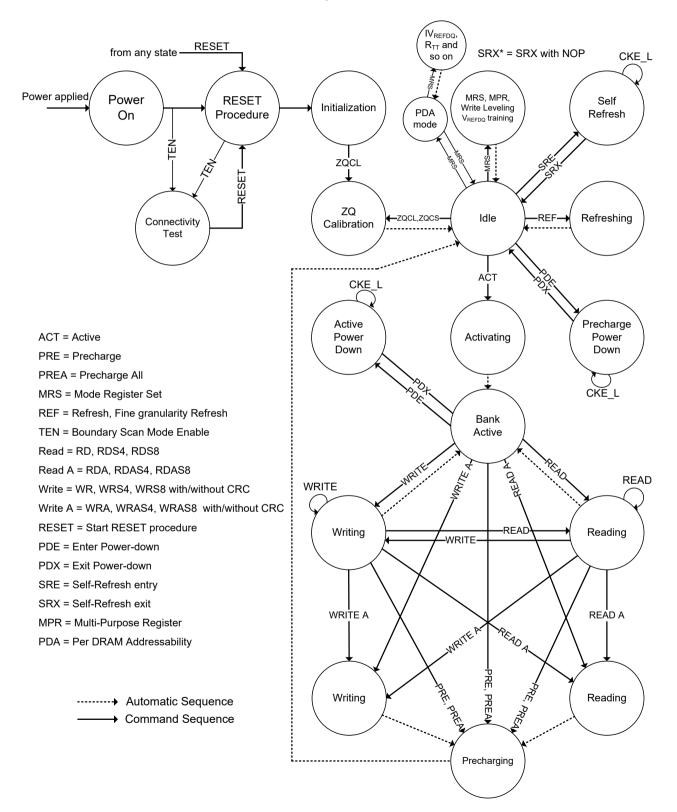

# Simplified State Diagram

This simplified State Diagram is intended to provide an overview of the possible state transitions and the commands to control them. In particular, situations involving more than on bank, the enabling or disabling of on-die termination, and some other events are not captured in full detail.

# Ball Descriptions

#### Table 3. Ball Details

| Symbol                          | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

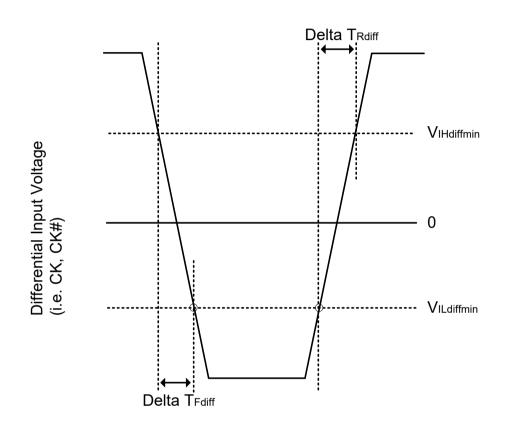

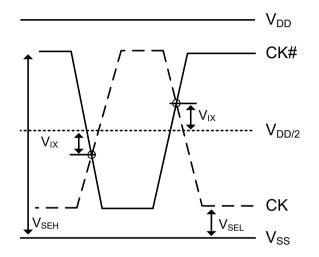

| CK, CK#                         | Input             | <b>Clock:</b> CK and CK# are differential clock inputs. All control and address input signals are sampled on the crossing of the positive edge of CK and the negative edge of CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

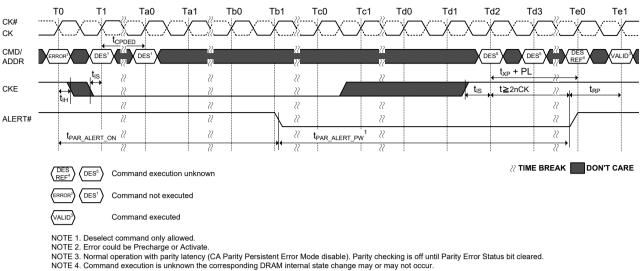

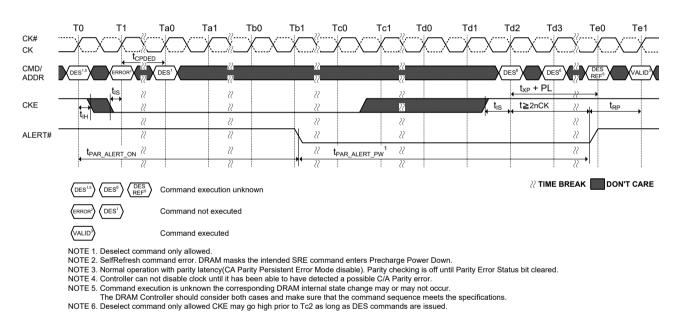

| CKE                             | Input             | <b>Clock Enable:</b> CKE high activates, and CKE low deactivates, internal clock signals<br>and device input buffers and output drivers. Taking CKE low provides Precharge<br>Power Down and Self-Refresh operation (all banks idle), or Active Power Down (row<br>Active in any bank). CKE is asynchronous for Self-Refresh exit. After $V_{REFCA}$ and<br>Internal DQ $V_{REF}$ have become stable during the power on and initialization sequence,<br>they must be maintained during all operations (including Self-Refresh). CKE must be<br>maintained high throughout read and write accesses. Input buffers, excluding CK,<br>CK#, ODT and CKE, are disabled during power down. Input buffers, excluding CKE,<br>are disabled during Self-Refresh. |

| CS#                             | Input             | <b>Chip Select:</b> All commands are masked when CS# is registered high. CS# provides for external Rank selection on systems with multiple Ranks. CS# is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

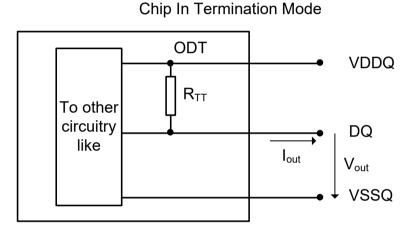

| ODT                             | Input             | <b>On Die Termination:</b> ODT (registered high) enables $R_{TT_NOM}$ termination resistance internal to the DDR4 SDRAM. When enabled, ODT is applied to each DQ, LDQS, LDQS#, UDQS, UDQS#, LDM, and UDM signal. The ODT pin will be ignored if MR1 is programmed to disable $R_{TT_NOM}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ACT#                            | Input             | <b>Activation Command Input:</b> ACT# defines the Activation command being entered along with CS#. The input into RAS#/A16, CAS#/A15 and WE#/A14 will be considered as Row Address A16, A15 and A14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RAS#/A16<br>CAS#/A15<br>WE#/A14 | Input             | <b>Command Inputs:</b> RAS#/A16, CAS#/A15 and WE#/A14 (along with CS#) define the command being entered. Those pins have multi function. For example, for activation with ACT# low, those are Addressing like A16, A15 and A14 but for non-activation command with ACT# high, those are Command pins for Read, Write and other command defined in command truth table.                                                                                                                                                                                                                                                                                                                                                                                   |

| LDM#/LDBI#<br>UDM#/UDBI#        | Input /<br>Output | <b>Input Data Mask and Data Bus Inversion:</b> DM# is an input mask signal for write data. Input data is masked when DM# is sampled low coincident with that input data during a Write access. DM# is sampled on both edges of DQS. DM is muxed with DBI function by Mode Register A10, A11, A12 setting in MR5. DBI# is an input /output identifying whether to store/output the true or inverted data. If DBI# is low the data will be stored/output after inversion inside the DDR4 SDRAM and not inverted if DBI# is high.                                                                                                                                                                                                                           |

| BG0                             | Input             | <b>Bank Group Inputs:</b> BG0 define to which bank group an Active, Read, Write or Precharge command is being applied. BG0 also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BA0-BA1                         | Input             | <b>Bank Address:</b> BA0-BA1 define to which bank an Active, Read, Write, or Precharge command is being applied. Bank address also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A0-A16                          | Input             | Address Inputs: Provide the row address (A0~A15) for Activate Commands and the column address (A0~A9) for Read/Write commands to select one location out of the memory array in the respective bank. (A10/AP, A12/BC#, RAS#/A16, CAS#/A15 and WE#/A14 have additional functions, see other rows. The address inputs also provide the op-code during Mode Register Set commands. A15 and A16 are used on some higher densities.                                                                                                                                                                                                                                                                                                                           |

| A10/AP                          | Input             | Auto-precharge: A10 is sampled during Read/Write commands to determine whether Autoprecharge should be performed to the accessed bank after the Read/Write operation. (high: Autoprecharge; low: no Autoprecharge). A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 low) or all banks (A10 high). If only one bank is to be precharged, the bank is selected by bank addresses.                                                                                                                                                                                                                                                                                                                    |

|                                    |                   | <b>Burst Chan</b> , A12/PC# is compled during Dood and Write commands to determine if                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A12/BC#                            | Input             | <b>Burst Chop:</b> A12/BC# is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (high, no burst chop; low: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                     |

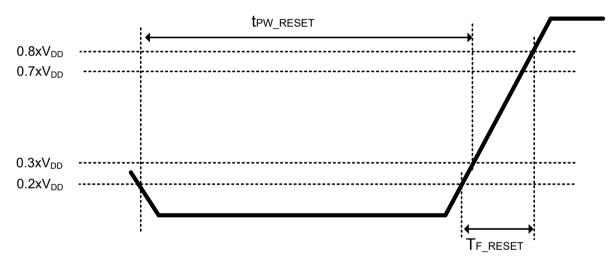

| Reset#                             | Input             | Active Low Asynchronous Reset: Reset is active when Reset# is low, and inactive when Reset# is high. Reset# must be high during normal operation. Reset# is a CMOS rail-to-rail signal with DC high and low at 80% and 20% of V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                     |

| DQ0-DQ15                           | Input /<br>Output | <b>Data Input/ Output:</b> Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0~DQ3 may indicate the internal $V_{REF}$ level during test via Mode Register Setting MR4 A4=high. During this mode, $R_{TT}$ should be set Hi-Z.                                                                                                                                                                                                                                                                            |

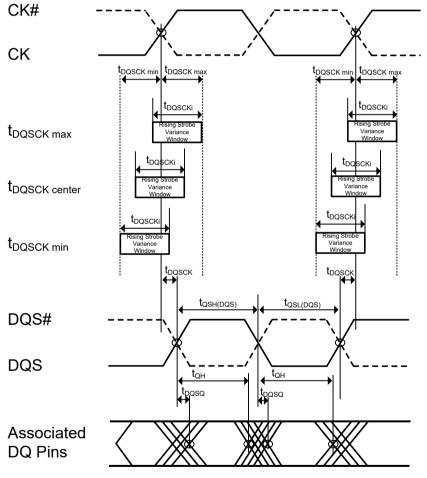

| LDQS,<br>LDQS#,<br>UDQS,<br>UDQS#, | Input /<br>Output | <b>Data Strobe:</b> output with read data, input with write data. Edge-aligned with read data, centered in write data. LDQS corresponds to the data on DQ0-DQ7; UDQS corresponds to the data on DQ8-DQ15. The data strobe LDQS and UDQS are paired with differential signals LDQS#, and UDQS#, respectively, to provide differential pair signaling to the system during reads and writes. DDR4 SDRAM supports differential data strobe only and does not support single-ended.                                                                                                     |

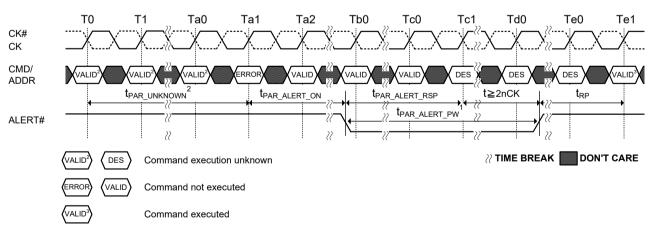

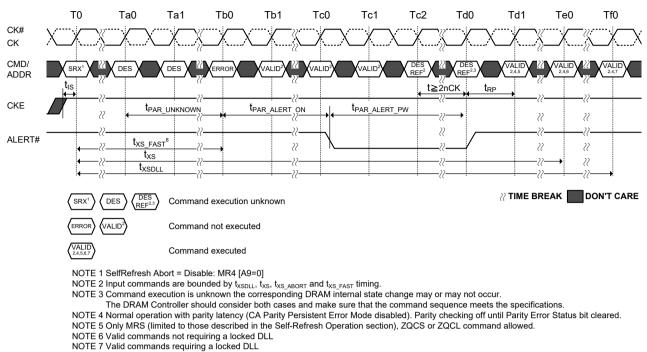

| PAR                                | Input             | <b>Command and Address Parity Input:</b> DDR4 Supports Even Parity check in DRAM with MR setting. Once it's enabled via Register in MR5, then DRAM calculates Parity with ACT#, RAS#/A16, CAS#/A15, WE#/A14, BG0, BA0-BA1, and A16-A0. Command and address inputs shall have parity check performed when commands are latched via the rising edge of CK and when CS# is low.                                                                                                                                                                                                        |

| Alert#                             | Input /<br>Output | Alert: It has multi functions such as CRC error flag, Command and Address Parity error flag as Output signal. If there is error in CRC, then Alert# goes low for the period time interval and goes back high. If there is error in Command Address Parity Check, then Alert# goes low for relatively long period until ongoing DRAM internal recovery transaction to complete. During Connectivity Test mode, this pin works as input. Using this signal or not is dependent on system. In case of not connected as Signal, Alert# Pin must be bounded to V <sub>DD</sub> on board. |

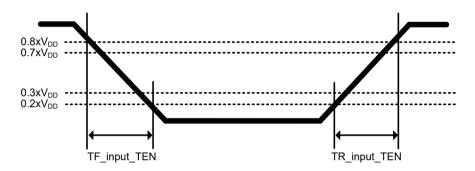

| TEN                                | Input             | <b>Connectivity Test Mode Enable:</b> Connectivity Test Mode is active when TEN is high, and inactive when TEN is low. TEN must be low during normal operation. TEN is a CMOS rail-to-rail signal with AC high and low at 80% and 20% of $V_{DD}$ (960mV for DC high and 240mV for DC low). Using this signal or not is dependent on System. This pin may be DRAM internally pulled low through a weak pull-down resistor to $V_{SS}$ .                                                                                                                                             |

| NC                                 | -                 | No Connect: These pins should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>DD</sub>                    | Supply            | Power Supply: +1.2V ±0.06V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub>                    | Supply            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

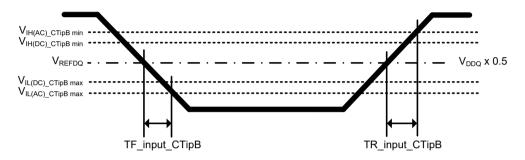

| $V_{DDQ}$                          | Supply            | DQ Power Supply: +1.2V ±0.06V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $V_{SSQ}$                          | Supply            | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{PP}$                           | Supply            | DRAM Activating Power Supply: 2.5V ( 2.375V min , 2.75V max)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

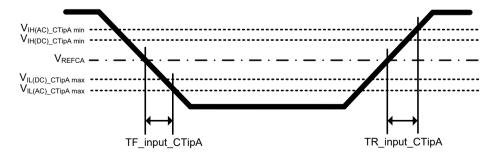

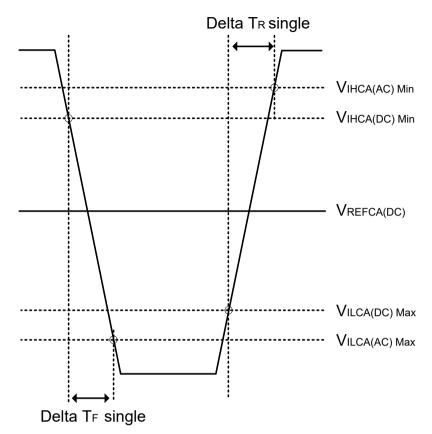

| $V_{REFCA}$                        | Supply            | Reference voltage for CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ZQ                                 | Supply            | Reference pin for ZQ calibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NOTE: Input only pin               | is (BG0, BA0-     | BA1, A0-A16, ACT#, RAS#/A16, CAS#/A15, WE#/A14, CS#, CKE, ODT, and RESET#) do not supply termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### Basic Functionality

The DDR4 SDRAM is a high-speed dynamic random-access memory internally organized with eight-banks (2 bank groups each with 4 banks). The DDR4 SDRAM uses a 8n prefetch architecture to achieve high-speed operation. The 8n prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR4 SDRAM consists of a single 8n-bit wide, four clock data transfer at the internal DRAM core and eight corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write operation to the DDR4 SDRAM are burst oriented, start at a selected location, and continue for a burst length of eight or a 'chopped' burst of four in a programmed sequence. Operation begins with the registration of an Activate Command, which is then followed by a Read or Write command. The address bits registered coincident with the Activate Command are used to select the bank and row to be activated (BG0 select the bank group; BA0-BA1 select the bank; A0-A15 select the row). The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst operation, determine if the auto precharge command is to be issued (via A10), and select BC4 or BL8 mode 'on the fly' (via A12) if enabled in the mode register.

Prior to normal operation, the DDR4 SDRAM must be powered up and initialized in a predefined manner. The following sections provide detailed information covering device reset and initialization, register definition, command descriptions, and device operation.

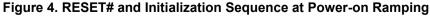

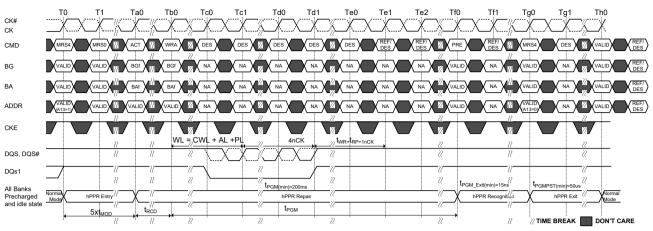

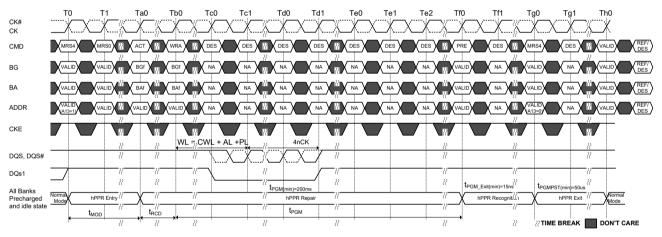

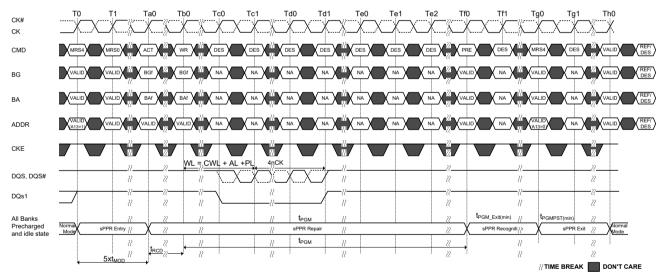

### **Reset and Initialization Procedure**

For power-up and reset initialization, in order to prevent DRAM from functioning improperly, default values for the following MR settings need to be defined:

Gear down mode (MR3 A[3]) : 0 = 1/2 Rate Per DRAM Addressability (MR3 A[4]) : 0 = Disable Max Power Saving Mode (MR4 A[1]): 0 = Disable CS# to Command/Address Latency (MR4 A[8:6]) : 000 = Disable CA Parity Latency Mode (MR5 A[2:0]) : 000 = Disable

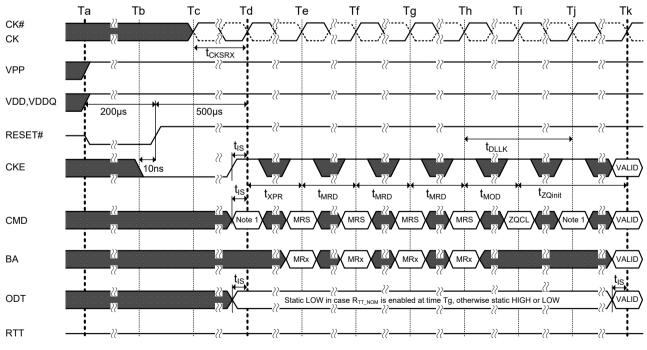

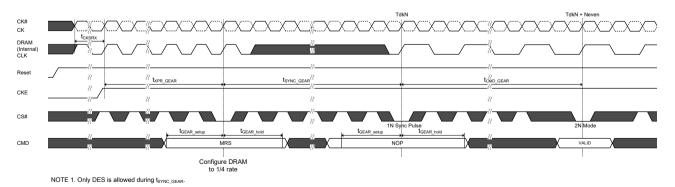

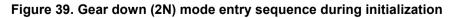

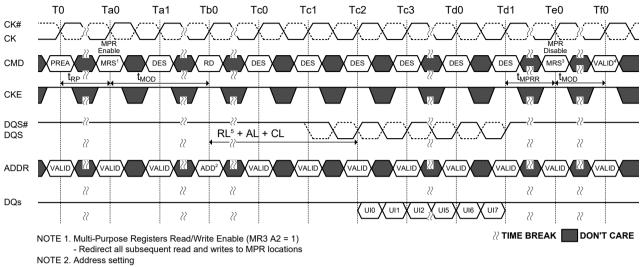

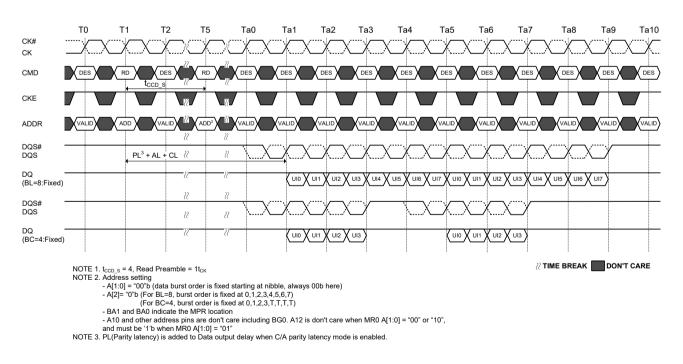

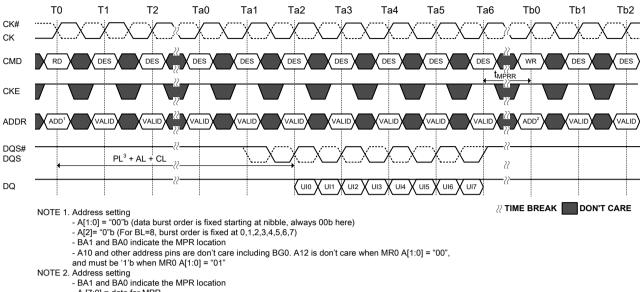

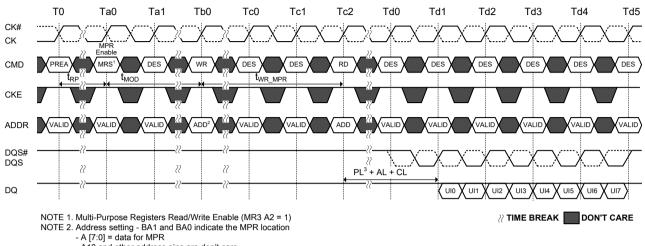

#### Power-up Initialization Sequence

The following sequence is required for Power up and Initialization:

- 1. Apply power (RESET# is recommended to be maintained below 0.2 x VDD; all other inputs may be undefined). RESET# needs to be maintained for minimum 200us with stable power. CKE is pulled LOW anytime before RESET# is being deasserted (MIN time 10ns). The power voltage ramp time between 300mV to VDD, min must be no greater than 200ms, and, during the ramp, VDD must be greater than or equal to VDDQ and (VDD - VDDQ) < 0.3V. VPP must ramp at the same time or earlier than VDD, and VPP must be equal to or higher than VDD at all times.

- VDD and VDDQ are driven from a single power converter output, AND

- The voltage levels on all pins other than VDD,VDDQ,VSS,VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side. In addition, VTT is limited to TBDV max once power ramp is finished, AND

VREFCA tracks TBD.

or

- Apply VDD without any slope reversal before or at the same time as VDDQ.

- Apply VDDQ without any slope reversal before or at the same time as VTT & VREFCA.

- Apply VPP without any slope reversal before or at the same time as VDD.

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side.

2.After Reset# is de-asserted, wait for another 500us until CKE becomes active. During this time, the DRAM will start internal initialization; this will be done independently of external clocks.

- 3. Clocks (CK, CK#) need to be started and stabilized for at least 10ns or 5t<sub>CK</sub> (which is larger) before CKE goes active. Since CKE is a synchronous signal, the corresponding setup time to clock (t<sub>IS</sub>) must be met. Also a Deselect command must be registered (with t<sub>IS</sub> set up time to clock) at clock edge Td. Once the CKE registered "high" after Reset, CKE needs to be continuously registered "high" until the initialization sequence is finished, including expiration of t<sub>DLLK</sub> and t<sub>ZQinit</sub>.

- 4. The DDR4 SDRAM keeps its on-die termination in high-impedance state as long as Reset# is asserted. Further, the SDRAM keeps its on-die termination in high impedance state after Reset# deassertion until CKE is registered high. The ODT input signal may be in undefined state until t<sub>IS</sub> before CKE is registered high. When CKE is registered high, the ODT input signal may be statically held at either low or high. If R<sub>TT\_NOM</sub> is to be enabled in MR1 the ODT input signal must be statically held low. In all cases, the ODT input signal remains static until the power up initialization sequence is finished, including the expiration of t<sub>DLLK</sub> and t<sub>zQinit</sub>.

- 5. After CKE is being registered high, wait minimum of Reset CKE Exit time, t<sub>XPR</sub>, before issuing the first MRS command to load mode register. (t<sub>XPR</sub>=Max(t<sub>XS</sub>, 5nCK)]

- 6. Issue MRS Command to load MR3 with all application settings (To issue MRS command to MR3, provide "low" to BG0, "high" to BA1, BA0)

- 7. Issue MRS command to load MR6 with all application settings (To issue MRS command to MR6, provide "low" to BA0, "high" to BG0, BA1)

- 8. Issue MRS command to load MR5 with all application settings (To issue MRS command to MR5, provide "low" to BA1, "high" to BG0, BA0)

- 9. Issue MRS command to load MR4 with all application settings (To issue MRS command to MR4, provide "Low" to BA1, BA0, "High" to BG0)

- 10. Issue MRS command to load MR2 with all application settings (To issue MRS command to MR2, provide "Low" to BG0, BA0, "High" to BA1)

- 11. Issue MRS command to load MR1 with all application settings (To issue MRS command to MR1, provide "Low" to BG0, BA1, "High" to BA0)

- 12. Issue MRS command to load MR0 with all application settings (To issue MRS command to MR0, provide "Low" to BG0, BA1, BA0)

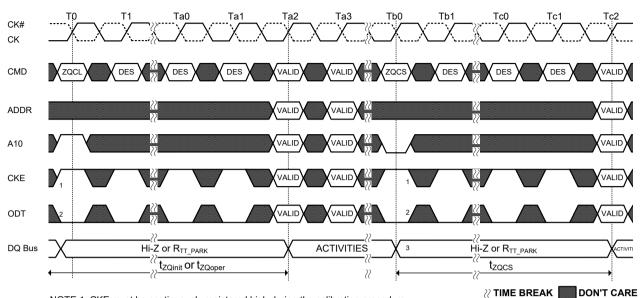

- 13. Issue ZQCL command to starting ZQ calibration.

- 14. Wait for both  $t_{\text{DLLK}}$  and  $t_{\text{ZQinit}}$  completed.

- 15. The DDR4 SDRAM is now ready for Read/Write training (include V<sub>REF</sub> training and Write leveling).

NOTE 1. From time point "Td" until "Tk " DES commands must be applied between MRS and ZQCL commands. NOTE 2. MRS Commands must be issued to all Mode Registers that have defined settings.

2 TIME BREAK DON'T CARE

#### V<sub>DD</sub> Slew rate at Power-up Initialization Sequence

#### Table 4. V<sub>DD</sub> Slew Rate

| Symbol              | Min.  | Max. | Units | Notes |

|---------------------|-------|------|-------|-------|

| V <sub>DD</sub> _sl | 0.004 | 600  | V/ms  | 1,2   |

| V <sub>DD</sub> _on | -     | 200  | ms    | 1,3   |

Notes:

1. Measurement made between 300mv and 80%  $V_{\mbox{\scriptsize DD}}$  minimum.

2. 20 MHz bandlimited measurement.

3. Maximum time to ramp  $V_{\text{DD}}$  from 300 mv to  $V_{\text{DD}}$  minimum.

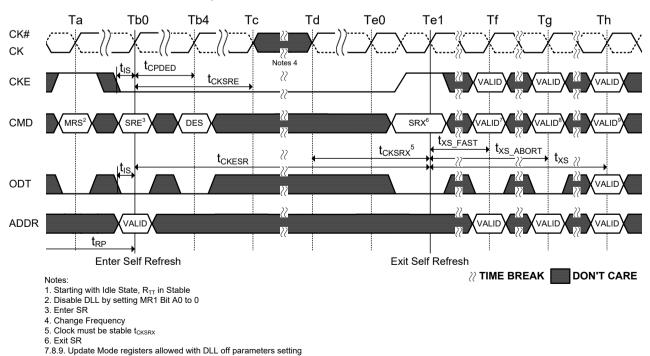

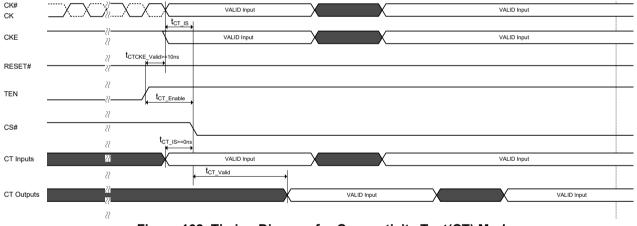

#### **Reset Initialization with Stable Power**

The following sequence is required for Reset at no power interruption initialization:

- 1. Asserted Reset# below 0.2 x V<sub>DD</sub> anytime when reset is needed (all other inputs may be undefined). Reset# needs to be maintained for minimum t<sub>PW\_Reset</sub>. CKE is pulled "low" before Reset# being de-asserted (min. time 10 ns).

- 2. Follow steps 2 to 10 in "Power-up Initialization Sequence".

- 3. The Reset sequence is now completed, DDR4 SDRAM is ready for Read/Write training (include V<sub>REF</sub> training and Write leveling)

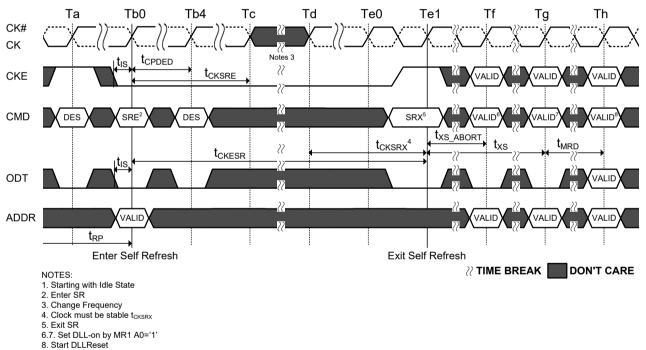

Figure 5. Reset Procedure at Power Stable

# **Operation Mode Truth Table**

Notes 1, 2, 3 and 4 apply to the entire Command Truth Table. Note 5 Applies to all Read/Write commands. [BG=Bank Group Address, BA=Bank Address, RA=Row Address, CA=Column Address, BC#=Burst Chop, X=Don't Care, V=Valid]. Table 5 Command Truth Table

| Function                                        | Symbol | CKE <sub>n-1</sub> | CKEn | CS# | ACT#   | RAS#<br>/A16 | CAS#<br>/A15 | WE#/<br>A14 | BG0    | BA0-1  | BC#/<br>A12 | A13,<br>A11 | A10/<br>AP | A0-A9  |

|-------------------------------------------------|--------|--------------------|------|-----|--------|--------------|--------------|-------------|--------|--------|-------------|-------------|------------|--------|

| Mode Register Set                               | MRS    | Н                  | Н    | L   | Н      | L            | L            | L           | BG     | BA     |             | OP (        | Code       |        |

| Refresh                                         | REF    | Н                  | Н    | L   | Н      | L            | L            | Н           | V      | V      | V           | V           | V          | V      |

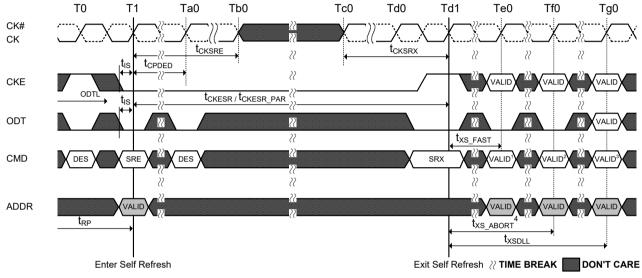

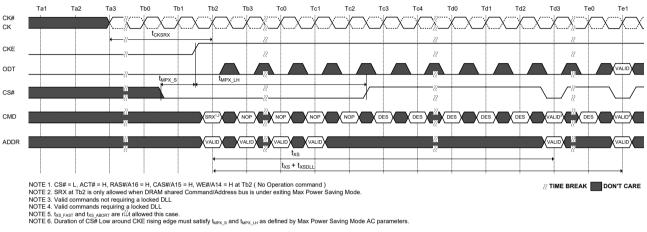

| Self Refresh Entry 7,9                          | SRE    | Н                  | L    | L   | Н      | L            | L            | Н           | V      | V      | V           | V           | V          | V      |

| Self Refresh Exit 7-10                          | SRX    | L                  | Н    | H   | X<br>H | X<br>H       | X<br>H       | X<br>H      | X<br>V | X<br>V | X<br>V      | X<br>V      | X<br>V     | X<br>V |

| Single Bank Precharge                           | PRE    | Н                  | Н    | L   | н      | L            | н            | L           | BG     | BA     | v           | V           | L          | V      |

| Precharge all Banks                             | PREA   | Н                  | Н    | L   | Н      | L            | Н            | L           | V      | V      | V           | V           | Н          | V      |

| RFU                                             | RFU    | Н                  | Н    | L   | н      | L            | Н            | Н           | RFU    | RFU    | RFU         | RFU         | RFU        | RFU    |

| Bank Activate                                   | ACT    | Н                  | Н    | L   | L      | RA           | RA           | RA          | BG     | BA     | RA          | RA          | RA         | RA     |

| Write (Fixed BL8 or BC4)                        | WR     | Н                  | Н    | L   | Н      | Н            | L            | L           | BG     | BA     | V           | V           | L          | CA     |

| Write (BC4, on the Fly)                         | WRS4   | Н                  | Н    | L   | Н      | Н            | L            | L           | BG     | BA     | L           | V           | L          | CA     |

| Write (BL8, on the Fly)                         | WRS8   | Н                  | Н    | L   | Н      | Н            | L            | L           | BG     | BA     | Н           | V           | L          | CA     |

| Write with Auto Precharge<br>(Fixed BL8 or BC4) | WRA    | н                  | Н    | L   | н      | Н            | L            | L           | BG     | BA     | V           | V           | н          | CA     |

| Write with Auto Precharge (BC4, on the Fly)     | WRAS4  | н                  | Н    | L   | н      | Н            | L            | L           | BG     | BA     | L           | V           | н          | CA     |

| Write with Auto Precharge<br>(BL8, on the Fly)  | WRAS8  | н                  | Н    | L   | н      | Н            | L            | L           | BG     | BA     | Н           | V           | н          | CA     |

| Read (Fixed BL8 or BC4)                         | RD     | Н                  | Н    | L   | Н      | Н            | L            | Н           | BG     | BA     | V           | V           | L          | CA     |

| Read (BC4, on the Fly)                          | RDS4   | Н                  | Н    | L   | Н      | Н            | L            | Н           | BG     | BA     | L           | V           | L          | CA     |

| Read (BL8, on the Fly)                          | RDS8   | Н                  | Н    | L   | Н      | Н            | L            | Н           | BG     | BA     | Н           | V           | L          | CA     |

| Read with Auto Precharge<br>(Fixed BL8 or BC4)  | RDA    | н                  | Н    | L   | н      | Н            | L            | Н           | BG     | BA     | V           | V           | н          | CA     |

| Read with Auto Precharge<br>(BC4, on the Fly)   | RDAS4  | н                  | Н    | L   | н      | Н            | L            | Н           | BG     | BA     | L           | V           | н          | CA     |

| Read with Auto Precharge<br>(BL8, on the Fly)   | RDAS8  | н                  | Н    | L   | н      | Н            | L            | Н           | BG     | BA     | Н           | V           | н          | CA     |

| No Operation                                    | NOP    | Н                  | Н    | L   | Н      | Н            | Н            | Н           | V      | V      | V           | V           | V          | V      |

| Device Deselected                               | DES    | Н                  | Н    | Н   | Х      | Х            | Х            | Х           | Х      | Х      | Х           | Х           | Х          | Х      |

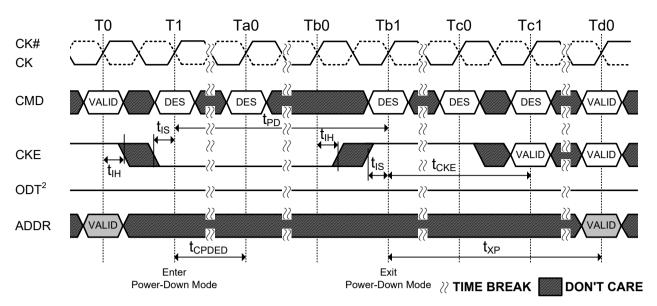

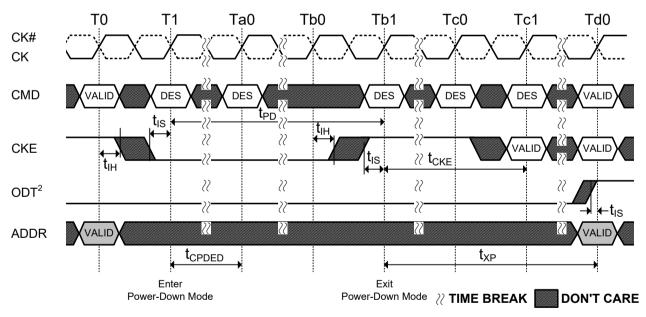

| Power Down Entry 6                              | PDE    | Н                  | L    | Н   | Х      | Х            | Х            | Х           | Х      | Х      | Х           | Х           | Х          | Х      |

| Power Down Exit <sup>6</sup>                    | PDX    | L                  | Н    | Н   | Х      | Х            | Х            | Х           | Х      | Х      | Х           | Х           | Х          | Х      |

| ZQ calibration Long                             | ZQCL   | Н                  | Н    | L   | Н      | Н            | Н            | L           | V      | V      | V           | V           | Н          | V      |

| ZQ calibration Short                            | ZQCS   | Н                  | Н    | L   | Н      | Н            | Н            | L           | V      | V      | V           | V           | L          | V      |

Note 1. All DDR4 SDRAM commands are defined by states of CS#, ACT#, RAS#/A16, CAS#/A15, WE#/A14 and CKE at the rising edge of the clock. The MSB of BG, BA, RA and CA are device density and configuration dependent. When ACT# = H; pins RAS#/A16, CAS#/A15, and WE#/A14 are used as command pins RAS#, CAS#, and WE# respectively. When ACT# = L; pins RAS#/A16, CAS#/A15, and WE#/A14 are used as address pins A16, A15, and A14 respectively.

Note 2. Reset# is low enable command which will be used only for asynchronous reset so must be maintained high during any function. Note 3. Bank Group addresses (BG) and Bank addresses (BA) determine which bank within a bank group to be operated upon. For MRS commands the BG

and BA selects the specific Mode Register location.

Note 4. "V" means "H or L (but a defined logic level)" and "X" means either "defined or undefined (like floating) logic level".

Note 5. Burst reads or writes cannot be terminated or interrupted and Fixed/on-the-Fly BL will be defined by MRS

Note 6. The Power Down Mode does not perform any refresh operation. Note 7. The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh.

Note 8. Controller guarantees self refresh exit to be synchronous.

Note 9. V<sub>PP</sub> and V<sub>REF</sub>(V<sub>REFCA</sub>) must be maintained during Self Refresh operation. Note 10. The No Operation (NOP) command may be used only when entering gear-down mode.

Note 11. Refer to the CKE Truth Table for more detail with CKE transition.

#### Table 6. CKE Truth Table

| Current State (2)                 | CKEn-1 <sup>(1)</sup> | CKEn <sup>(1)</sup>     | Command n <sup>(3)</sup><br>RAS#, CAS#, WE#, CS# | Action n <sup>(3)</sup>    | Notes       |

|-----------------------------------|-----------------------|-------------------------|--------------------------------------------------|----------------------------|-------------|

| Power-Down                        | L                     | L                       | Х                                                | Maintain Power-Down        | 14,15       |

| Fower-Down                        | L                     | Н                       | Deselect                                         | Power-Down Exit            | 11,14       |

| Calf Dafaab                       | L                     | L                       | Х                                                | Maintain Self-Refresh      | 15,16       |

| Self-Refresh                      | L                     | Н                       | Deselect                                         | Self-Refresh Exit          | 8,12,16     |

| Bank(s) Active H L Deselect Activ |                       | Active Power-Down Entry | 11,13,14                                         |                            |             |

| Reading                           | Н                     | L                       | Deselect                                         | Power-Down Entry           | 11,13,14,17 |

| Writing                           | Н                     | L                       | Deselect                                         | Power-Down Entry           | 11,13,14,17 |

| Precharging                       | Н                     | L                       | Deselect                                         | Power-Down Entry           | 11,13,14,17 |

| Refreshing                        | Н                     | L                       | Deselect                                         | Precharge Power-Down Entry | 11          |

| All Banks Idle                    | Н                     | L                       | Deselect                                         | Precharge Power-Down Entry | 11,13,14,18 |

| All Darks Idle                    | Н                     | L                       | Refresh                                          | Self-Refresh               | 9,13,18     |

|                                   |                       | See Comma               | and Truth Table for additional comma             | nd details                 | 10          |

#### Notes:

1. CKEn is the logic state of CKE at clock edge n; CKEn-1 was the state of CKE at the previous clock edge.

2. Current state is defined as the state of the DDR4 SDRAM immediately prior to clock edge n.

3. Command n is the command registered at clock edge n, and Action n is a result of command n, ODT is not included here.

4. All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document.

5. The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh.

During any CKE transition (registration of CKE H → L or CKE L → H) the CKE level must be maintained until 1nCK prior to t<sub>CKEmin</sub> being satisfied (at which time CKE may transition again).

7. Deselect and NOP are defined in the Command Truth Table.

8. On Self Refresh Exit Deselect commands must be issued on every clock edge occurring during the t<sub>xs</sub> period. Read or ODT commands may be issued only after t<sub>xsDLL</sub> is satisfied.

9. Self Refresh mode can only be entered from the All Banks Idle state.

10. Must be a legal command as defined in the Command Truth Table.

11. Valid commands for Power Down Entry and Exit are Deselect only.

12. Valid commands for Self Refresh Exit are Deselect only. except for Gear Down mode. NOP is allowed for the mode.

13. Self Refresh cannot be entered during Read or Write operations. For a detailed list of restrictions see section "Self-Refresh Operation" and see section "Power-Down Modes".

14. The Power Down does not perform any refresh operations.

15. "X" means "don't care" (including floating around  $V_{REF}$ ) in Self Refresh and Power Down. It also applies to Address pins.

16.  $V_{PP}$  and  $V_{REF}$  ( $V_{REFCA}$ ) must be maintained during Self Refresh operation.

17. If all banks are closed at the conclusion of the read, write or precharge command, then Precharge Power Down is entered, otherwise Active Power Down is entered.

18. 'Idle state' is defined as all banks are closed (t<sub>RP</sub>, t<sub>DAL</sub>, etc. satisfied), no data bursts are in progress, CKE is high, and all timings from previous operations are satisfied (t<sub>MRD</sub>, t<sub>MOD</sub>, t<sub>RFC</sub>, t<sub>ZQinit</sub>, t<sub>ZQOPEr</sub>, t<sub>ZQCS</sub>, etc.) as well as all Self Refresh exit and Power Down Exit parameters are satisfied (t<sub>XS</sub>, t<sub>XP</sub>, etc).

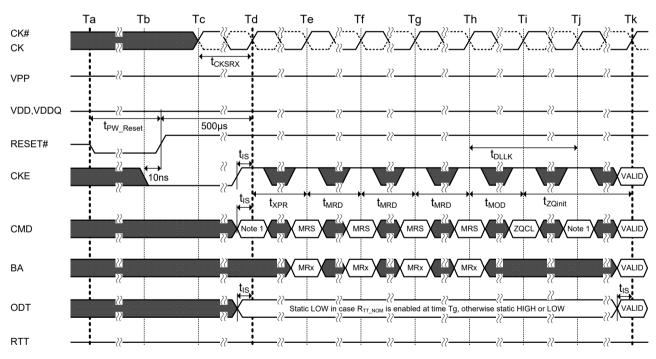

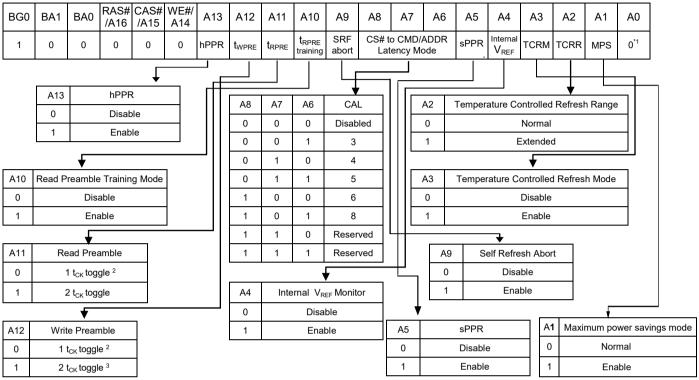

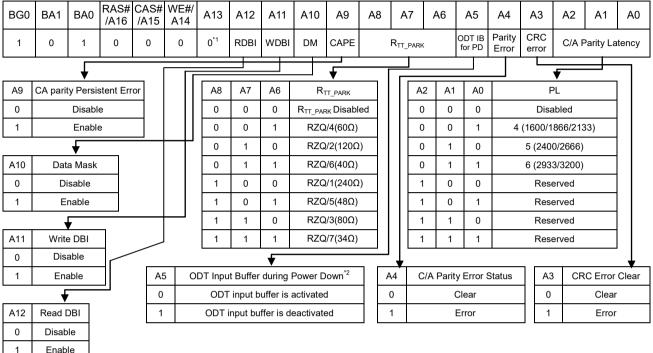

#### **Programming the Mode Registers**

For application flexibility, various functions, features, and modes are programmable in seven Mode Registers, provided by the DDR4 SDRAM, as user defined variables and they must be programmed via a Mode Register Set (MRS) command. The mode registers are divided into various fields depending on the functionality and/or modes. As not all the Mode Registers (MR*n*) have default values defined, contents of Mode Registers must be initialized and/or re-initialized, i.e. written, after power up and/or reset for proper operation. Also the contents of the Mode Registers can be altered by re-executing the MRS command during normal operation. When programming the mode registers, even if the user chooses to modify only a sub-set of the MRS fields, all address fields within the accessed mode register must be redefined when the MRS command is issued. MRS command and DLL Reset do not affect array contents, which means these commands can be executed any time after power-up without affecting the array contents. MRS Commands can be issued only when DRAM is at idle state. The mode register set command cycle time, t<sub>MRD</sub> is required to complete the write operation to the mode register and is the minimum time required between two MRS commands shown in the t<sub>MRD</sub> timing figure.

Figure 6. t<sub>MRD</sub> timing

Some of the Mode Register setting affect to address/command/control input functionality. These case, next MRS command can be allowed when the function updating by current MRS command completed.

The MRS commands that do not apply  $t_{MRD}$  timing to next MRS command. These MRS command input cases have unique MR setting procedure, so refer to individual function description.

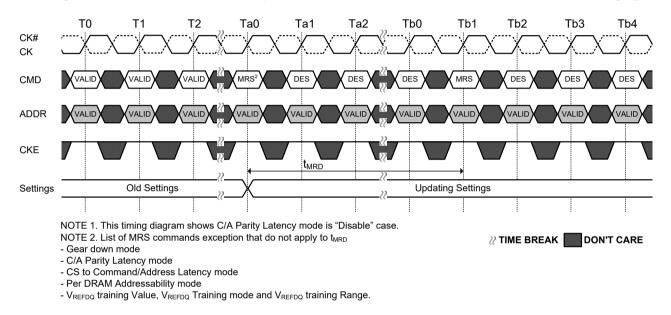

The most MRS command to Non-MRS command delay, t<sub>MOD</sub>, is required for the DRAM to update the features, and is the minimum time required from an MRS command to a non-MRS command excluding DES, as shown in the  $t_{MOD}$  timing figure.

Some of the mode register setting cases, function updating takes longer than t<sub>MOD</sub>. The MRS commands that do not apply t<sub>MOD</sub> timing to next valid command excluding DES is listed in Note 2 of t<sub>MOD</sub> timing figure. These MRS command input cases have unique MR setting procedure, so refer to individual function description.

NOTE 1. This timing diagram shows C/A Parity Latency mode is "Disable" case. NOTE 2. List of MRS commands exception that do not apply to  $t_{MOD}$

- DLL Enable, DLL Reset

- V<sub>REFDQ</sub> training Value, internal V<sub>REF</sub> Monitor, V<sub>REFDQ</sub> Training mode and V<sub>REFDQ</sub> training Range

- Gear down mode

- Per DRAM addressability mode

- CA Parity mode

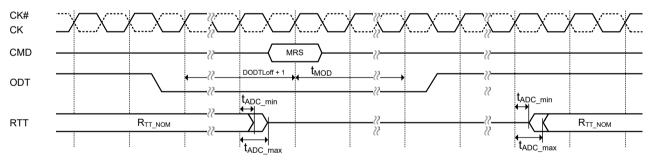

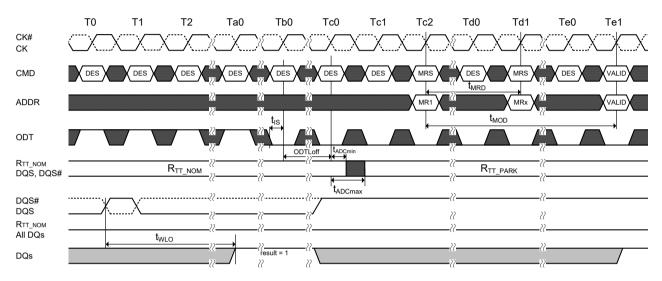

#### Figure 7. t<sub>MOD</sub> timing

NOTE 1. This timing diagram shows C/A Parity Latency mode is "Disable" case.

NOTE 2. When an MRS command mentioned in this note affects  $R_{TT_NOM}$  turn on timings,  $R_{TT_NOM}$  turn off timings and  $R_{TT_NOM}$  value, this means the MR register value changes. The ODT signal should set to be low for at least DODTLoff +1 clock before their affecting MRS command is issued and remain low until t<sub>MOD</sub> expires. The following MR registers affects R<sub>TT\_NOM</sub> turn on timings, R<sub>TT\_NOM</sub> turn off timings and R<sub>TT NOM</sub> value and it requires ODT to be low when an MRS command change the MR register value. If there are no change the MR register value that correspond to commands mentioned in this note, then ODT signal is not require to be low.

- DLL control for precharge power down - Additive latency and CAS read latency

- DLL enable and disable

- CAS write latency

- CA Parity mode

- Gear down mode

- R<sub>TT\_NOM</sub>

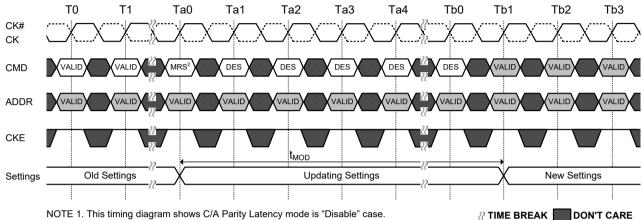

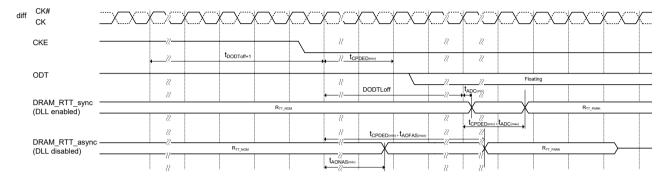

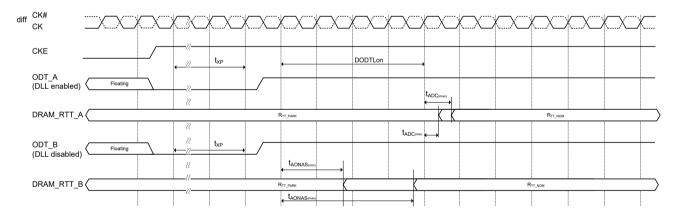

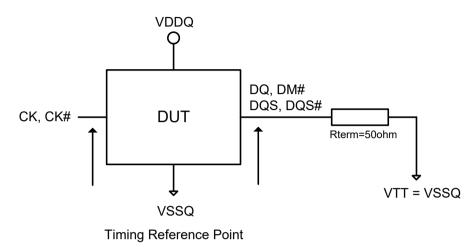

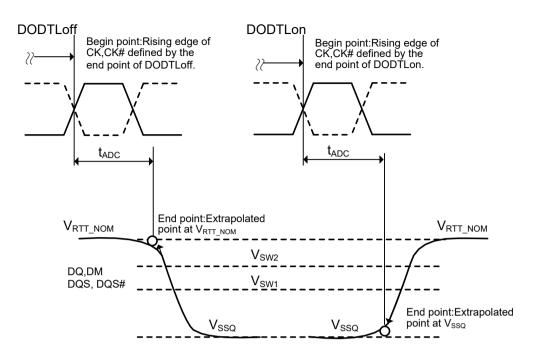

#### Figure 8. ODT Status at MRS affecting ODT turn-on/off timing

The mode register contents can be changed using the same command and timing requirements during normal operation as long as the device is in idle state, i.e., all banks are in the precharged state with t<sub>BP</sub> satisfied, all data bursts are completed and CKE is high prior to writing into the mode register. If R<sub>TT NOM</sub> function is intended to change (enable to disable and vice versa) or already enabled in DRAM MR, ODT signal must be registered Low ensuring R<sub>TT NOM</sub> is in an off state prior to MRS command affecting R<sub>TT\_NOM</sub> turn-on and off timing. The ODT signal may be registered high after t<sub>MOD</sub> has expired. ODT signal is a don't care during MRS command if DRAM R<sub>TT NOM</sub> function is disabled in the mode register prior and after an MRS command.

| Table | 7  | MR0    | Definition |

|-------|----|--------|------------|

| Iable | 1. | IVITAU | Deminion   |

|     | 57.IVI   |       |              | CAS#   |              |        | 1           | 1 1      |       |               |                           |             |       |    |     |    |            |       |         |        | 1   |    |  |

|-----|----------|-------|--------------|--------|--------------|--------|-------------|----------|-------|---------------|---------------------------|-------------|-------|----|-----|----|------------|-------|---------|--------|-----|----|--|

| BG0 | BA1      | BA0   | RAS#<br>/A16 |        | VVE#/<br>A14 | A13    | A12         | A11      | A10   | A9            | A                         | 3           | A7    | A6 | A5  | A  | <b>\</b> 4 | A3    | A2      | A1     | A0  |    |  |

| 0   | 0        | 0     | 0            | 0      | 0            | 0*1    | 0*1         | WR & RT  |       | <b>3</b> *2,3 | <sup>2,3</sup> DLL TM Rst |             |       | CL | *4  |    | BT         | CL*4  | E       | BL     |     |    |  |

|     | <b>•</b> |       |              |        |              |        |             |          |       |               |                           |             | ┘_    |    |     |    |            |       |         |        |     |    |  |

|     | A8       | וח    | ▼<br>L Rese  | et     |              | A7     | ▼<br>Test M | lode     |       | A3            | Read                      | l Bur       | st Ty | be | Ιг  | A1 | A0         | )     |         | BL     |     |    |  |

|     | 0        |       | No           |        |              | 0      | Norm        |          |       | 0             |                           |             | ntial |    |     | 0  | 0          |       | 8 (     | Fixed) |     |    |  |

|     | 1        |       | Yes          |        |              |        |             |          |       | 1             |                           | '<br>nterle |       |    |     | 0  | 1          | E     | C4 or 8 | ,      |     |    |  |

|     |          |       |              |        |              |        |             |          |       |               |                           |             |       |    |     | 1  | 0          |       |         | (Fixed | • • |    |  |

|     |          |       |              | Г      |              |        |             |          | J     |               |                           |             |       |    |     | 1  | 1          |       | Re      | served |     |    |  |

|     |          |       |              | . ↓    |              |        |             |          |       |               |                           |             |       |    | ↓ └ |    | 1          |       |         |        |     |    |  |

|     | A11      | A10   | A9           | W      | R            | RT     | C           |          |       |               | A6                        | A5          | A4    | A2 |     | (  | CAS        | Laten |         |        |     |    |  |

|     | 0        | 0     | 0            | 1(     | 0            | 5      |             |          |       |               | 0                         | 0           | 0     | 0  |     |    |            | 9     |         |        |     |    |  |

|     | 0        | 0     | 1            | 12     | 2            | 6      |             |          |       |               | 0                         | 0           | 0     | 1  |     | 10 |            |       |         |        |     |    |  |

|     | 0        | 1     | 0            | 14     | 4            | 7      |             |          |       |               | 0                         | 0           | 1     | 0  |     |    |            |       |         |        |     |    |  |

|     | 0        | 1     | 1            | 10     | 6            | 8      |             |          |       |               | 0                         | 0           | 1     | 1  |     | 12 |            |       |         |        |     |    |  |

|     | 1        | 0     | 0            | 18     |              | 9      |             |          |       |               |                           |             | 0     | 1  | 0   | 0  |            |       |         | 13     |     |    |  |

|     | 1        | 0     | 1            | 20     | -            | 10     |             |          |       |               |                           |             |       |    | 0   | 1  | 0          | 1     |         |        |     | 14 |  |

|     | 1        | 1     | 0            | 24     |              | 12     |             |          |       |               | 0                         | 1           | 1     | 0  |     |    |            | 15    |         |        |     |    |  |

|     | Write    | Recov | /ery an      | d Read | to Pre       | charge | for au      | to prech | narge |               | 0                         | 1           | 1     | 1  |     |    |            | 16    |         |        |     |    |  |

|     |          |       |              |        |              |        |             |          |       |               | 1                         | 0           | 0     | 0  |     |    |            | 18    |         |        |     |    |  |

|     |          |       |              |        |              |        |             |          |       | _             | 1                         | 0           | 0     | 1  |     |    |            | 20    |         |        |     |    |  |

|     |          |       |              |        | 1            | 0      | 1           | 0        | -     |               |                           | 22          |       | _  |     |    |            |       |         |        |     |    |  |

|     |          |       |              |        |              |        |             |          |       | _             | 1                         | 0           | 1     | 1  | _   |    |            | 24*5  |         | _      |     |    |  |

|     |          |       |              |        |              |        |             |          |       |               | 1                         | 1           | 0     | 0  | +   |    | Res        | erved |         | _      |     |    |  |

|     |          |       |              |        |              |        |             |          |       |               | 1                         | 1           | 0     | 1  | +   |    |            | 17    |         | _      |     |    |  |

|     |          |       |              |        |              | _      | 1           | 1        | 1     | 0             |                           |             |       | 19 |     | _  |            |       |         |        |     |    |  |

|     |          |       |              |        |              |        |             |          |       |               | 1                         | 1           | 1     | 1  |     |    |            | 21    |         |        |     |    |  |

Note 1 Reserved for future use and must be programmed to 0 during MR.

Note 2 WR (write recovery for autoprecharge)min in clock cycles is calculated by dividing tWR(in ns) by tCK(in ns) and rounding up to the next integer:WRmin[cycles] = Roundup(tWR[ns] / tCK[ns]). The WR value in the mode register must be programmed to be equal or larger than WRmin. The programmed WR value is used with tRP to determine tDAL. Note 3 The table shows the encodings for Write Recovery and internal Read command to Precharge command delay. For actual Write recovery timing, please refer to AC timing table.

Note 4 The table only shows the encodings for a given Cas Latency. For actual supported Cas Latency, please refer to speed bin tables for each frequency.

Note 5 When CL is equal to 24 or more than 24, AL does not support CL-1.

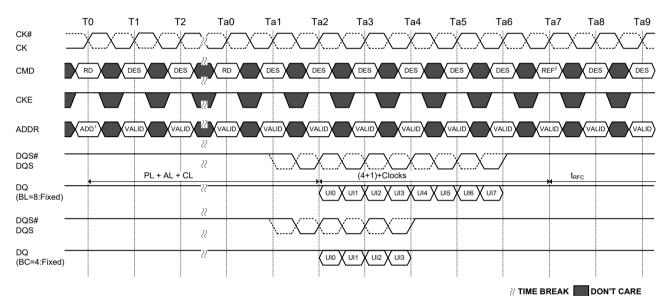

# CAS Latency

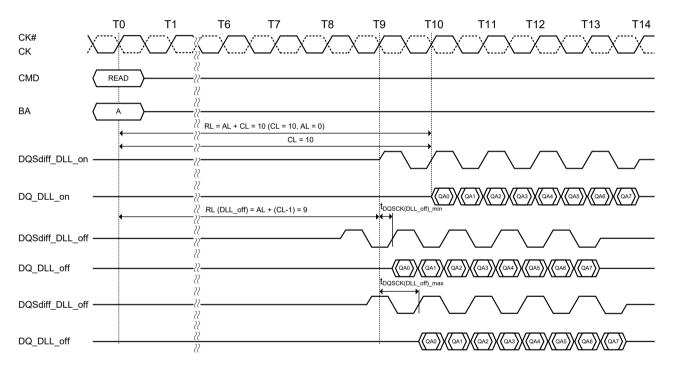

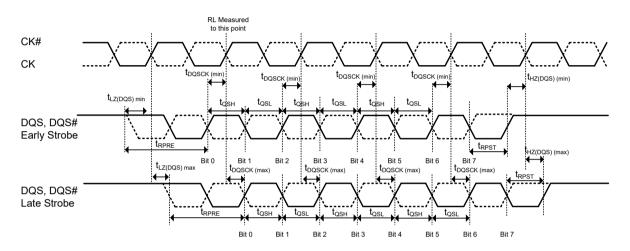

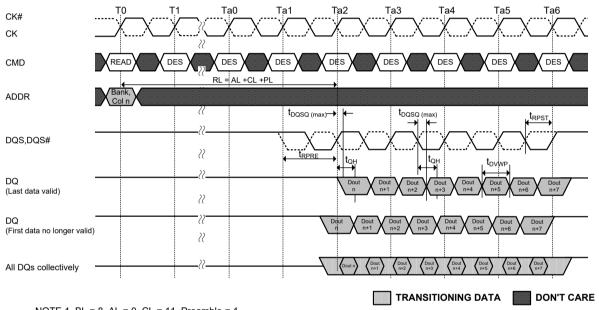

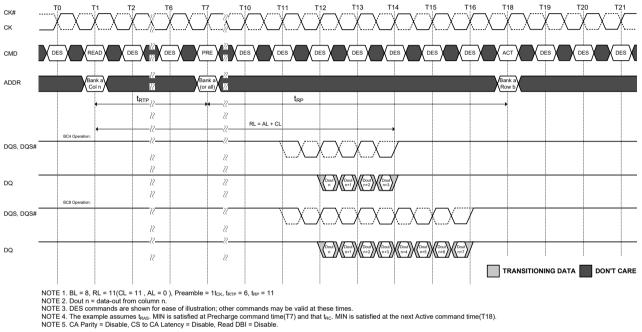

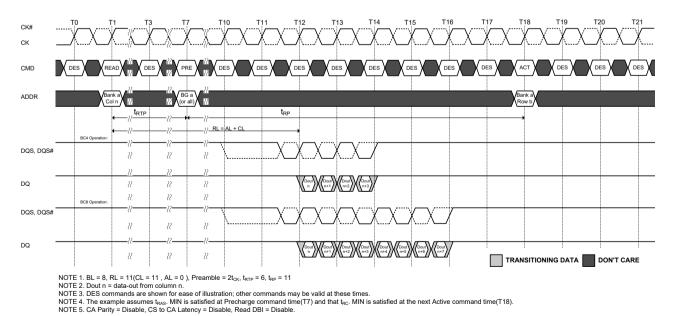

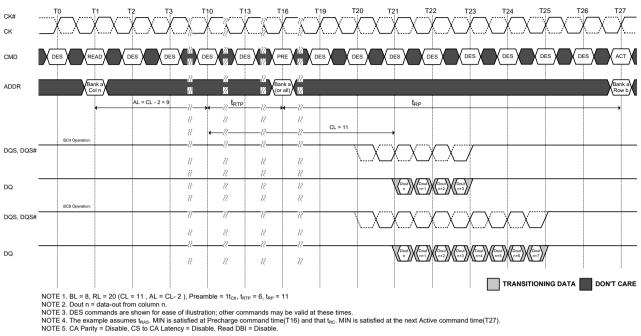

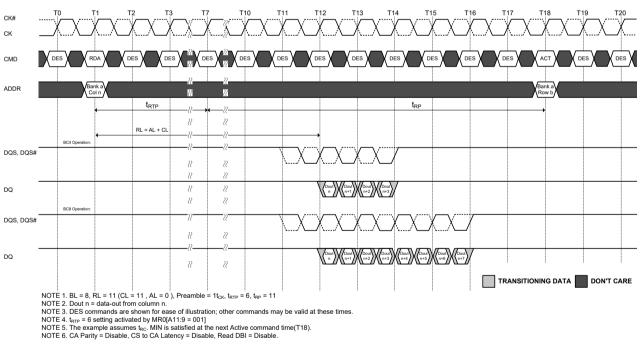

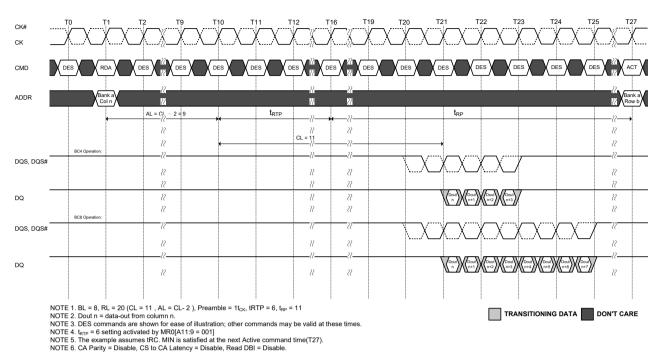

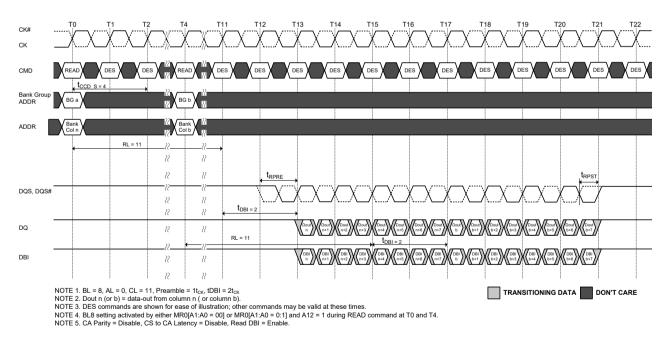

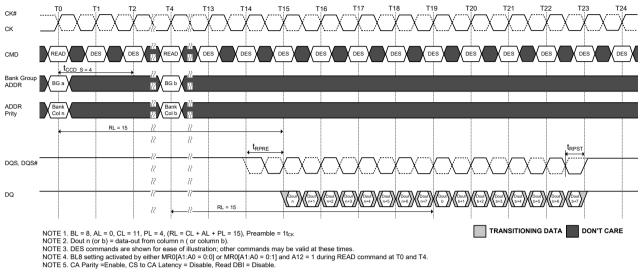

The CAS latency (CL) setting is defined in the MR0 Register Definition table. CAS latency is the delay, in clock cycles, between the internal read command and the availability of the first bit of output data. The device does not support half-clock latencies. The overall read latency (RL) is defined as additive latency (AL) + CAS latency (CL): RL = AL + CL.

### Test Mode

The normal operating mode is selected by MR0[7] and all other bits set to the desired values shown in the MR0 Register Definition table. Programming MR0[7] to a value of 1 places the device into a DRAM manufacturer-defined test mode to be used only by the manufacturer, not by the end user. No operations or functionality is specified if MR0[7] = 1.

### **DLL Reset**

The DLL reset bit is self-clearing, meaning that it returns to the value of 0 after the DLL reset function has been issued. After the DLL is enabled, a subsequent DLL reset should be applied. Any time the DLL reset function is used,  $t_{\text{DLLK}}$  must be met before functions requiring the DLL can be used. (For example, Read commands or ODT synchronous operations).

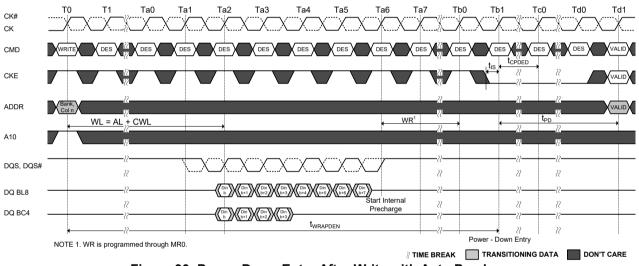

### Burst Length, Type and Order

Accesses within a given burst may be programmed to sequential or interleaved order. The burst type is selected via bit A3 of Mode Register MR0. The ordering of accesses within a burst is determined by the burst length, burst type, and the starting column address as shown in the following table. The burst length is defined by bits A0-A1 of Mode Register MR0. Burst length options include fixed BC4, fixed BL8, and 'on the fly' which allows BC4 or BL8 to be selected coincident with the registration of a Read or Write command via A12/BC#.

| Burst Length | Read/Write | Starting | Column | Address | Burst type = Sequential | burst type = Interleaved | Note     |

|--------------|------------|----------|--------|---------|-------------------------|--------------------------|----------|

| Burst Length | Reau/wille | A2       | A1     | A0      | (decimal) A3=0          | (decimal) A3=1           | NOLE     |

|              |            | 0        | 0      | 0       | 0, 1, 2, 3, T, T, T, T  | 0, 1, 2, 3, T, T, T, T   |          |

|              |            | 0        | 0      | 1       | 1, 2, 3, 0, T, T, T, T  | 1, 0, 3, 2, T, T, T, T   |          |

|              |            | 0        | 1      | 0       | 2, 3, 0, 1, T, T, T, T  | 2, 3, 0, 1, T, T, T, T   |          |

|              | Read       | 0        | 1      | 1       | 3, 0, 1, 2, T, T, T, T  | 3, 2, 1, 0, T, T, T, T   | 1, 2, 3  |

| 4 Chop       | Reau       | 1        | 0      | 0       | 4, 5, 6, 7, T, T, T, T  | 4, 5, 6, 7, T, T, T, T   | 1, 2, 3  |

| 4 Спор       |            | 1        | 0      | 1       | 5, 6, 7, 4, T, T, T, T  | 5, 4, 7, 6, T, T, T, T   |          |

|              |            | 1        | 1      | 0       | 6, 7, 4, 5, T, T, T, T  | 6, 7, 4, 5, T, T, T, T   |          |

|              |            | 1        | 1      | 1       | 7, 4, 5, 6, T, T, T, T  | 7, 6, 5, 4, T, T, T, T   |          |

|              | Write      | 0        | V      | V       | 0, 1, 2, 3, X, X, X, X  | 0, 1, 2, 3, X, X, X, X   | 1, 2, 4, |

|              | Willo      | 1        | V      | V       | 4, 5, 6, 7, X, X, X, X  | 4, 5, 6, 7, X, X, X, X   | 5        |

|              |            | 0        | 0      | 0       | 0, 1, 2, 3, 4, 5, 6, 7  | 0, 1, 2, 3, 4, 5, 6, 7   |          |

|              |            | 0        | 0      | 1       | 1, 2, 3, 0, 5, 6, 7, 4  | 1, 0, 3, 2, 5, 4, 7, 6   |          |

|              |            | 0        | 1      | 0       | 2, 3, 0, 1, 6, 7, 4, 5  | 2, 3, 0, 1, 6, 7, 4, 5   |          |

|              | Read       | 0        | 1      | 1       | 3, 0, 1, 2, 7, 4, 5, 6  | 3, 2, 1, 0, 7, 6, 5, 4   | 2        |

| 8            | Read       | 1        | 0      | 0       | 4, 5, 6, 7, 0, 1, 2, 3  | 4, 5, 6, 7, 0, 1, 2, 3   | 2        |

|              |            | 1        | 0      | 1       | 5, 6, 7, 4, 1, 2, 3, 0  | 5, 4, 7, 6, 1, 0, 3, 2   |          |

|              |            | 1        | 1      | 0       | 6, 7, 4, 5, 2, 3, 0, 1  | 6, 7, 4, 5, 2, 3, 0, 1   |          |

|              |            | 1        | 1      | 1       | 7, 4, 5, 6, 3, 0, 1, 2  | 7, 6, 5, 4, 3, 2, 1, 0   |          |

|              | Write      | V        | V      | V       | 0, 1, 2, 3, 4, 5, 6, 7  | 0, 1, 2, 3, 4, 5, 6, 7   | 2, 4     |

#### Table 8. Burst Type and Burst Order

Notes:

1. In case of burst length being fixed to 4 by MR0 setting, the internal write operation starts two clock cycles earlier than for the BL8 mode. This means that the starting point for t<sub>WR</sub> and t<sub>WTR</sub> will be pulled in by two clocks. In case of burst length being selected on-the-fly via A12/BC#, the internal write operation starts at the same point in time like a burst of 8 write operation. This means that during on-the-fly control, the starting point for t<sub>WR</sub> and t<sub>WTR</sub> will not be pulled in by two clocks.

2. 0...7 bit number is value of CA[2:0] that causes this bit to be the first read during a burst.

3. T: Output driver for data and strobes are in high impedance.

4. V: a valid logic level (0 or 1), but respective buffer input ignores level on input pins.

5. X: Don't Care.

# Write Recovery (WR)/Read-to-Precharge (RTP)

The programmed write recovery (WR) value is used for the auto precharge feature along with  $t_{RP}$  to determine  $t_{DAL}$ . WR for auto precharge (MIN) in clock cycles is calculated by dividing  $t_{WR}$  (in ns) by  $t_{CK}$  (in ns) and rounding to the next integer:

The WR value must be programmed to be equal to or larger than  $t_{WR}$  (MIN). When both DM and write CRC are enabled in the mode register, the device calculates CRC before sending the write data into the array;  $t_{WR}$  values will change when enabled. If there is a CRC error, the device blocks the Write operation and discards the data.

Internal Read-to-Precharge (RTP) command delay for auto precharge (MIN) in clock cycles is calculated by dividing  $t_{RTP}$  (in ns) by  $t_{CK}$  (in ns) and rounding to the next integer:

The RTP value in the mode register must be programmed to be equal to or larger than RTP (MIN). The programmed RTP value is used with  $t_{RP}$  to determine the ACT timing to the same bank.

| Table | 9. M | IR1 D    | efinit       | tion             |               |           |                    |                 |     |                                                                         |        |                    |          |                 |                  |           |         |             |         |

|-------|------|----------|--------------|------------------|---------------|-----------|--------------------|-----------------|-----|-------------------------------------------------------------------------|--------|--------------------|----------|-----------------|------------------|-----------|---------|-------------|---------|

| BG0   | BA1  | BA0      | RAS#<br>/A16 |                  | # WE#/<br>A14 | A13       | A12                | A11             | A10 | A9                                                                      | A8     | A7                 | A6       | A5              | A4               | A3        | A2      | A1          | A0      |

| 0     | 0    | 1        | 0            | 0                | 0             | 0*1       | Qoff <sup>*2</sup> | 0 <sup>*1</sup> |     | R <sub>TT_NOM</sub> WL 0 <sup>*1</sup> 0 <sup>*1</sup> AL <sup>*4</sup> |        | WL(                |          | L <sup>*4</sup> | 0                | DI        | DLL     |             |         |

|       |      | L        |              |                  |               |           | _ <b>_</b> _       |                 |     |                                                                         |        | ┛ᢏ                 |          |                 |                  |           |         | <u> </u>    |         |

| A12   | 2    | Qof      | f            |                  | A7 V          | /rite Lev | veling E           | nable           | AC  | )                                                                       | DLL Er | able               | ור       | A2              | A1 0             | utput Dri | ver Imp | ▼<br>edance | Control |

| 0     | Outp | ut buffe | r enable     | ed               | 0             | D         | isable             |                 | 0   |                                                                         | Disab  | le <sup>*3</sup>   |          | 0               | 0                |           | ZQ/7(3  |             |         |

| 1     | Outp | ut buffe | r disable    | ed               | 1             | E         | nable              |                 | 1   |                                                                         | Enat   | ole                |          | 0               | 1                | R         | ZQ/5(4  | -8Ω)        |         |

|       |      |          |              |                  |               |           |                    |                 |     |                                                                         |        |                    |          | 1               | 0                |           | Reser   | ved         |         |

|       |      |          |              | Г                |               |           |                    |                 | 1   |                                                                         |        |                    |          | 1               | 1                |           | Reser   | ved         |         |

|       | 1    |          | -            | •                |               |           |                    |                 |     |                                                                         |        |                    | <u> </u> |                 |                  |           |         |             | 7       |

| A10   | A9   | A8       |              | R <sub>TT_</sub> | MOM           |           |                    |                 |     |                                                                         |        | A4                 | A3       |                 | Additive Latency |           |         |             |         |

| 0     | 0    | 0        | RT           | T_NOM            | Disable       | •         |                    |                 |     |                                                                         |        | 0 0 0(AL disabled) |          |                 |                  |           |         |             |         |

| 0     | 0    | 1        | R            | ZQ/4(6           | 0Ω)           |           |                    |                 |     |                                                                         |        | 0                  | 1        |                 |                  | CL-1      | 1       |             |         |

| 0     | 1    | 0        | R            | ZQ/2(1           | 20Ω)          |           |                    |                 |     |                                                                         |        | 1                  | 0        |                 |                  | CL-2      |         |             |         |

| 0     | 1    | 1        | R            | ZQ/6(4           | 0Ω)           |           |                    |                 |     |                                                                         |        | 1                  | 1        |                 |                  | Reserv    | ed      |             | 1       |

| 1     | 0    | 0        | R            | ZQ/1(2           | 40Ω)          |           |                    |                 |     |                                                                         |        |                    | •        |                 |                  |           |         |             | _       |

| 1     | 0    | 1        | R            | ZQ/5(4           | 8Ω)           |           |                    |                 |     |                                                                         |        |                    |          |                 |                  |           |         |             |         |

| 1     | 1    | 0        | R            | ZQ/3(8           | 0Ω)           |           |                    |                 |     |                                                                         |        |                    |          |                 |                  |           |         |             |         |

| 1     | 1    | 1        | R            | ZQ/7(3           | 4Ω)           |           |                    |                 |     |                                                                         |        |                    |          |                 |                  |           |         |             |         |

Note 1. Reserved for future use and must be programmed to 0 during MRS.

Note 2 .Outputs disabled - DQs, DQSs, DQSs.

Note 3. States reversed to "0 as Disable" with respect to DDR4.

Note 4. Not allowed when 1/4 rate geardown mode is enabled.

# DLL Enable/DLL Disable

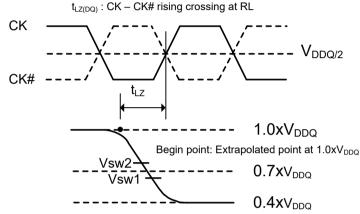

The DLL must be enabled for normal operation and is required during power-up initialization and upon returning to normal operation after having the DLL disabled. During normal operation (DLL enabled with MR1[0]) the DLL is automatically disabled when entering the Self Refresh operation and is automatically reenabled upon exit of the Self Refresh operation. Any time the DLL is enabled and subsequently reset,  $t_{DLLK}$  clock cycles must occur before a Read or Synchronous ODT command can be issued to allow time for the internal clock to be synchronized with the external clock. Failing to wait for synchronization to occur may result in a violation of the  $t_{DQSCK}$ ,  $t_{AON}$ , or  $t_{AOF}$  parameters.

During t<sub>DLLK</sub>, CKE must continuously be registered High. The device does not require DLL for any Write operation, except when R<sub>TT WR</sub> is enabled and the DLL is required for proper ODT operation.

The direct ODT feature is not supported during DLL off mode. The ODT resistors must be disabled by continuously registering the ODT pin Low and/or by programming the  $R_{TT_NOM}$  bits MR1[10:8] = 000 via an MRS command during DLL off mode.

The dynamic ODT feature is not supported in DLL off mode; to disable dynamic ODT externally, use the MRS command to set  $R_{TT WR}$ , MR2[11:9] = 00.

# **Output Driver Impedance Control**

The output driver impedance of the device is selected by MR1[2:1].

### ODT R<sub>TT\_NOM</sub> Values

The device is capable of providing three different termination values:  $R_{TT\_PARK}$ ,  $R_{TT\_NOM}$ , and  $R_{TT\_WR}$ . The nominal termination value,  $R_{TT\_NOM}$ , is programmed in MR1. A separate value,  $R_{TT\_WR}$ , may be programmed in MR2 to enable a unique  $R_{TT}$  value when ODT is enabled during Write operations. The  $R_{TT\_WR}$  value can be applied during Write commands even when  $R_{TT\_NOM}$  is disabled. A third  $R_{TT}$  value,  $R_{TT\_PARK}$ , is programmed in MR5.  $R_{TT\_PARK}$  provides a termination value when the ODT signal is Low.

#### Additive Latency

The Additive Latency (AL) operation is supported to make command and data bus efficient for sustainable bandwidths in the device. In this operation, the device allows a Read or Write command (either with or without auto precharge) to be issued immediately after the Activate command. The command is held for the time of AL before it is issued inside the device. Read latency (RL) is controlled by the sum of the AL and CAS latency (CL) register settings. Write latency (WL) is controlled by the sum of the AL and CAS Write latency (CWL) register settings. Additive Latency is not supported for x16 device.

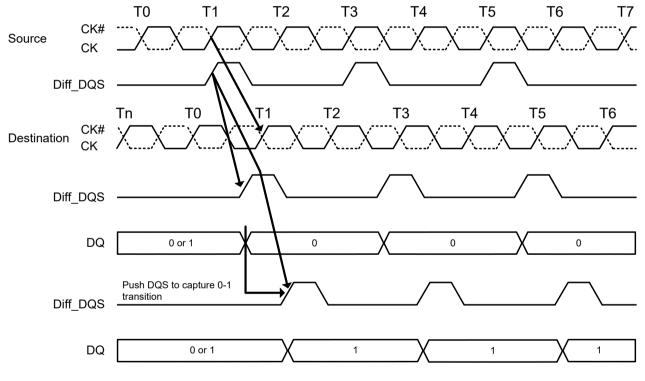

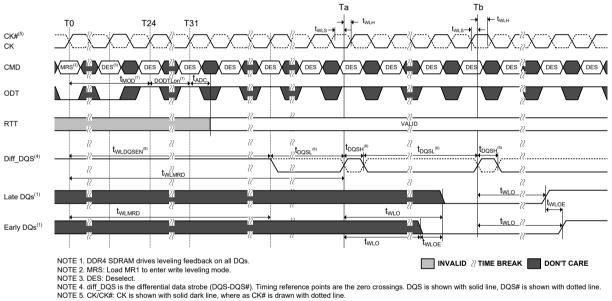

#### Write Leveling

For better signal integrity, the device uses fly-by topology for the commands, addresses, control signals, and clocks. Fly-by topology benefits from a reduced number of stubs and their lengths, but it causes flight-time skew between clock and strobe at every DRAM on the DIMM. This makes it difficult for the controller to maintain tDQSS, tDSS, and tDSH specifications. Therefore, the device supports a write leveling feature that allows the controller to compensate for skew.

### **Output Disable**

The device outputs may be enabled/disabled by MR1[12] as shown in the MR1 Register Definition table. When MR1[12] is enabled (MR1[12] = 1) all output pins (such as DQ and DQS) are disconnected from the device, which removes any loading of the output drivers. For example, this feature may be useful when measuring module power. For normal operation, set MR1[12] to 0.

| BG0           | BA1   | BA0    | RAS#<br>/A16 | CAS#<br>/A15 | WE#/<br>A14               | A13  | A12                                                                                                                                                                           | A11    | A10                | A9     | A8       | A7       | A6      | A5     | A4                   | A3     | A2     | A1  | AC |

|---------------|-------|--------|--------------|--------------|---------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|--------|----------|----------|---------|--------|----------------------|--------|--------|-----|----|

| 0             | 1     | 0      | 0            | 0            | 0                         | 0*1  | Write<br>CRC                                                                                                                                                                  |        | R <sub>TT_WR</sub> |        | 0*1      | LP/      | ASR     |        | CWL                  |        | 0*1    | 0*1 | 0* |

|               |       | Ţ.     |              |              |                           |      |                                                                                                                                                                               |        |                    |        |          | •        |         | •      |                      |        |        | •   |    |

| A12 Write CRC |       |        | A11          | A10          | A10 A9 R <sub>TT_WR</sub> |      |                                                                                                                                                                               |        |                    |        |          |          |         |        |                      |        |        |     |    |

| 0 Disable     |       |        | 0            | 0            | 0                         |      |                                                                                                                                                                               |        |                    |        |          |          |         |        |                      |        |        |     |    |

| 1             |       | Enable |              | 0            | 0                         | 1    |                                                                                                                                                                               |        |                    |        |          |          |         |        |                      |        |        |     |    |

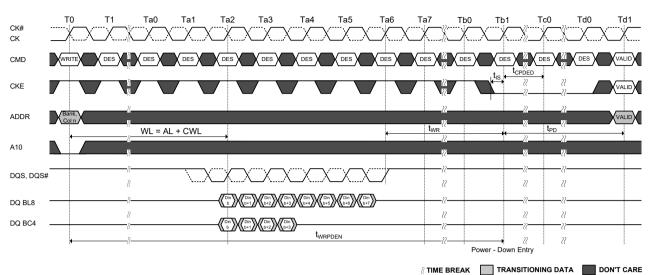

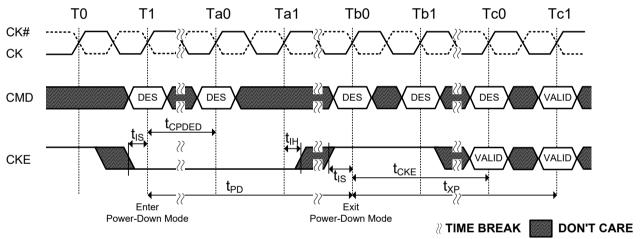

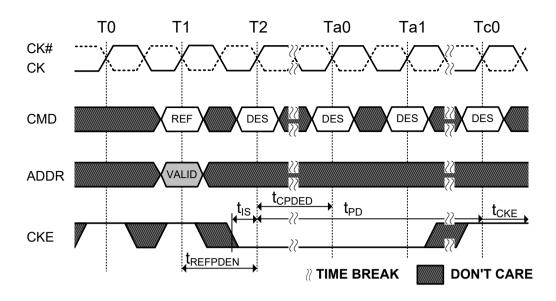

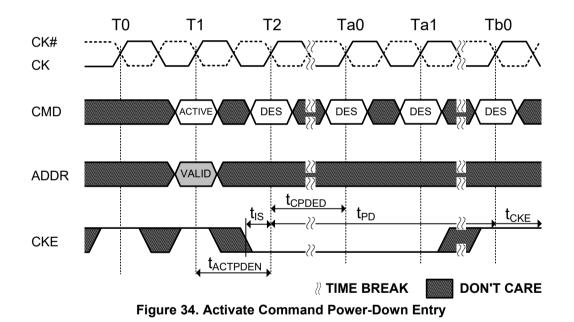

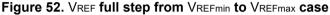

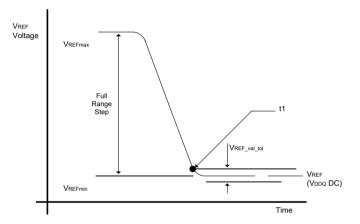

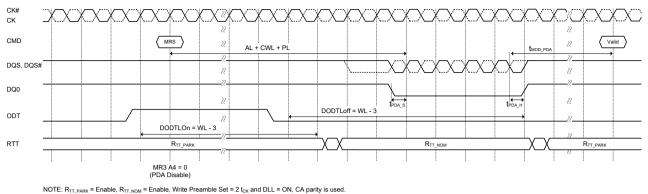

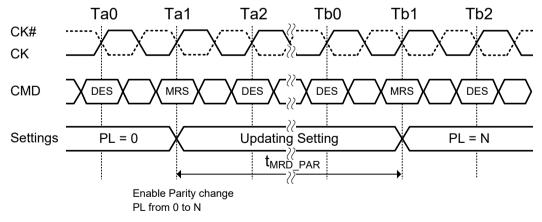

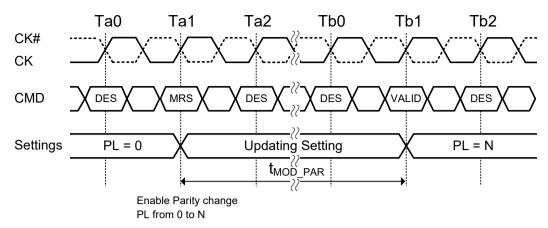

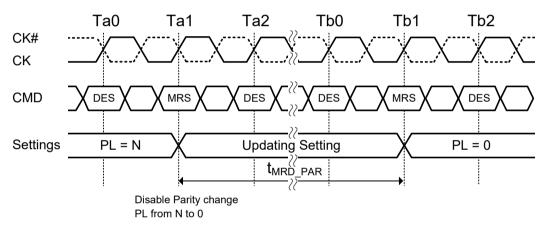

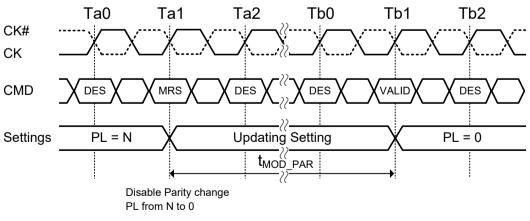

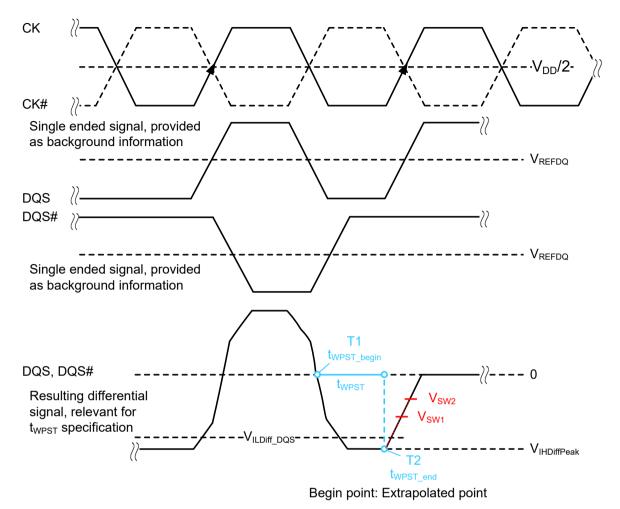

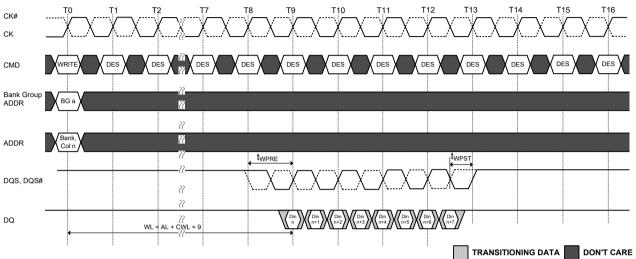

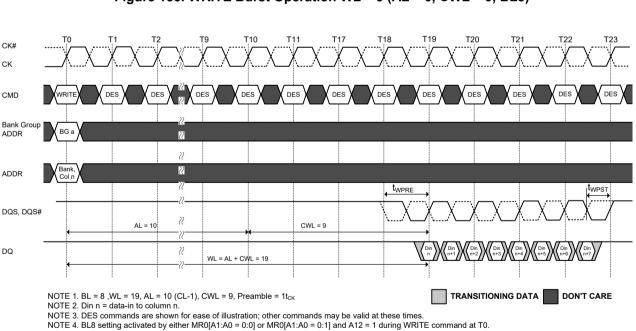

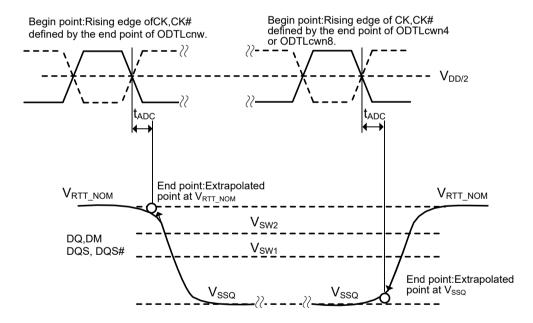

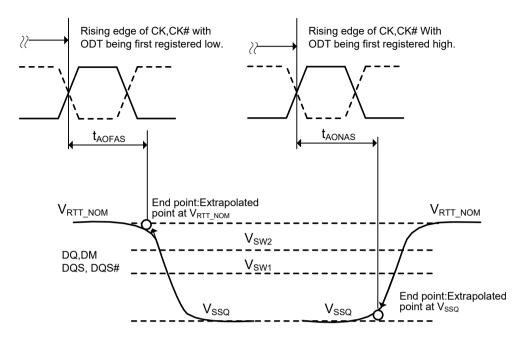

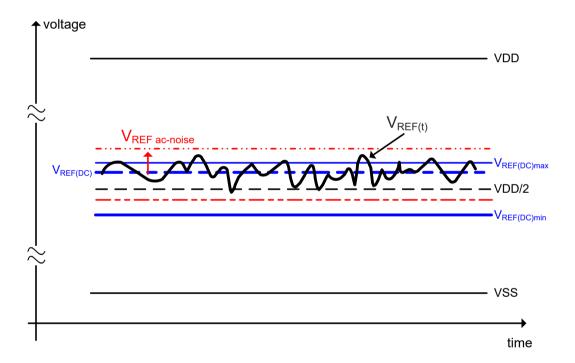

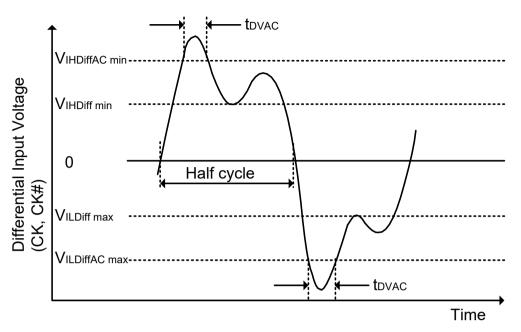

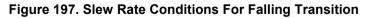

|               |       |        |              | 0            | 1                         | 0    |                                                                                                                                                                               |        |                    | RZQ/   | 1(2400   | 2)       |         |        |                      |        |        |     |    |