# AS6C1016 64K X 16 BIT LOW POWER CMOS SRAM

### **REVISION HISTORY**

| Revision<br>Rev. 1.0<br>Rev. 1.1 | Description Initial Issue Revised FEATURES & ORDERING INFORMATION Lead free and green package available to Green package available Added packing type in ORDERING INFORMATION Deleted Tsolder in ABSOLUTE MAXIMUM RATINGS Revised PACKAGE OUTLINE DIMENSION in page 11 | Issue Date<br>Nov.19.2008<br>May.6.2010 |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Rev. 1.2                         | Revised V <sub>DR</sub> to 1.5V<br>Revised <b>ORDERING INFORMATION</b> in page 12                                                                                                                                                                                      | Aug.30.2010                             |

| Rev. 1.3<br>Rev. 1.4             | Revised typo in <b>PRODUCT FAMILY</b> page 1 Deleted E Grade                                                                                                                                                                                                           | Oct.4.2010<br>Aug.9.2011                |

| Rev. 1.5                         | Revised typo page 0 ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                           | Sep 29 2015                             |

|                                  | Revised typo Page 3 - ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                         |                                         |

|                                  | Revised Page 12 - Package option from T(TSOPII) to Z (TSOP II)                                                                                                                                                                                                         |                                         |

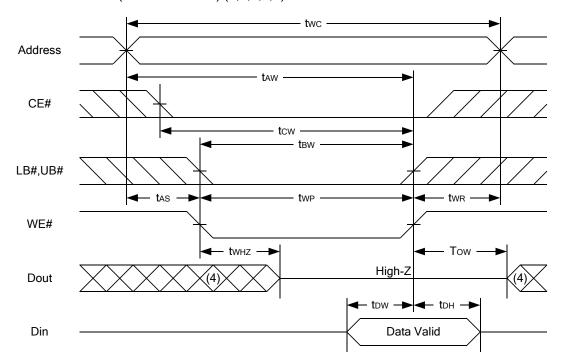

#### WRITE CYCLE 1 (WE# Controlled) (1,2,3,5,6)

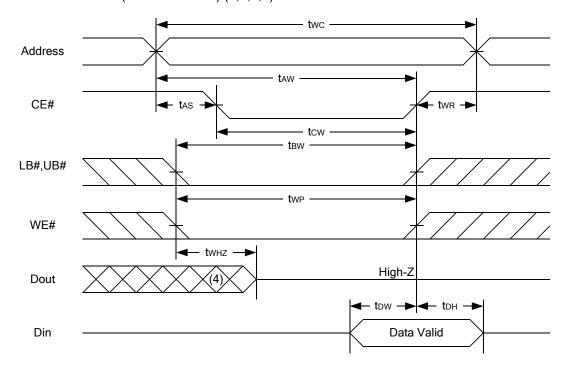

#### WRITE CYCLE 2 (CE# Controlled) (1,2,5,6)

6

### AS6C1016 64K X 16 BIT LOW POWER CMOS SRAM

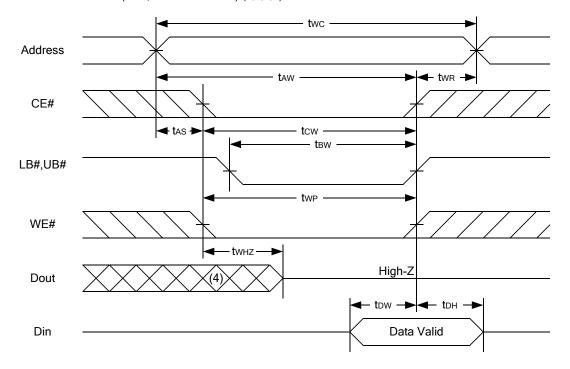

#### WRITE CYCLE 3 (LB#,UB# Controlled) (1,2,5,6)

#### Notes:

- 1.WE#,CE#, LB#, UB# must be high during all address transitions.

2.A write occurs during the overlap of a low CE#, low WE#, LB# or UB# = low.

- 3.During a WE# controlled write cycle with OE# low, twp must be greater than twnz + tow to allow the drivers to turn off and data to be placed on the bus.

- 4. During this period, I/O pins are in the output state, and input signals must not be applied.

5. If the CE#, LB#, UB# low transition occurs simultaneously with or after WE# low transition, the outputs remain in a high impedance

- 6.tow and twHz are specified with CL = 5pF. Transition is measured  $\pm 500mV$  from steady state.

## AS6C1016 64K X 16 BIT LOW POWER CMOS SRAM

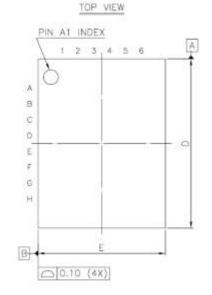

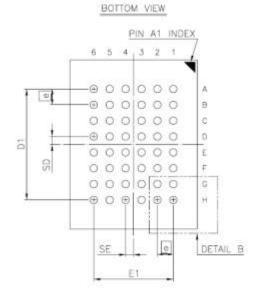

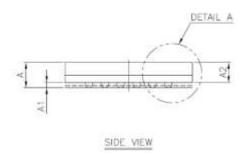

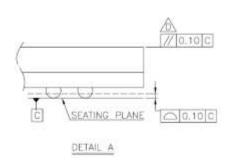

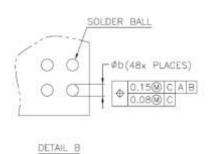

#### 48-ball 6mm × 8mm TFBGA Package Outline Dimension

|          | SYM. | DIMENSION<br>(mm) |           | DIMENSION<br>(inch) |           |           |       |  |

|----------|------|-------------------|-----------|---------------------|-----------|-----------|-------|--|

|          |      | MIN.              | NOM.      | MAX.                | MIN.      | NOM.      | MAX.  |  |

|          | Α    | -                 | -         | 1.20                | -         | -         | 0.047 |  |

|          | AT   | 0.20              | 0.25      | 0.30                | 0.008     | 0.010     | 0.012 |  |

|          | A2   |                   | -         | 0.94                | _         | _         | 0.037 |  |

|          | b    | 0.30              | 0.35      | 0.40                | 0.012     | 0.014     | 0.016 |  |

| AA       | D    | 7.95              | 8.00      | 8.05                | 0.313     | 0.315     | 0.317 |  |

|          | D1   | 5                 | .25 BS    | BSC 0.207 BSC       |           | SC.       |       |  |

| <u> </u> | E    | 5.95              | 6.00      | 6.05                | 0.234     | 0.236     | 0.238 |  |

|          | E1.  | - 3               | 3.75 BSC  |                     |           | 148 BS    | SC    |  |

|          | SE   |                   | 0.375 TYP |                     |           | 0.015 TYP |       |  |

|          | SD   |                   | 0.375 TYP |                     | 0.015 TYP |           |       |  |

|          | [e]  |                   | .75 BS(   | 3                   | .0        | 030 BS    | SC    |  |

#### NOTE:

- 1. CONTROLLING DIMENSION ; MILLIMETER.

- 2. REFERENCE DOCUMENT : JEDEC MO-207.

THIS PAGE IS LEFT BLANK INTENTIONALLY.